N° d'ordre NNT : 2023ECDL0026

THÈSE de DOCTORAT DE L'ÉCOLE CENTRALE DE LYON

opérée au sein de l'Université de Lyon

École Doctorale n°160

Électronique Électrotechnique et Automatique (EEA)

**Discipline** : Électronique, Micro et Nanoélectronique, Optique et Laser

Soutenue publiquement le 5 juillet 2023, par :

**Mayeul Cantan**

---

**Calcul éco-énergétique avec matériaux

ferroélectriques intégrés pour les

systèmes embarqués et à la périphérie de

réseau**

---

Devant le jury composé de :

|                     |                                         |                                        |                       |

|---------------------|-----------------------------------------|----------------------------------------|-----------------------|

| Maneux, Cristell    | Professeur des Universités <sup>a</sup> | Université de Bordeaux / IMS Bordeaux  | Présidente            |

| Niemier, Michael    | Full Professor                          | University of Notre Dame, Indiana, USA | Rapporteur            |

| Portal, Jean-Michel | Professeur des Universités <sup>a</sup> | Aix-Marseille Université / IM2NP       | Rapporteur            |

| O'Connor, Ian       | Professeur des Universités <sup>a</sup> | École Centrale de Lyon / INL           | Directeur de thèse    |

| Deleruyelle, Damien | Professeur des Universités <sup>a</sup> | INSA Lyon / INL                        | Co-directeur de thèse |

| Marchand, Cédric    | Maître de Conférences <sup>a</sup>      | École Centrale de Lyon / INL           | Co-directeur de thèse |

| Slesazeck, Stefan   | Senior Researcher                       | NaMLab, Dresden, Allemagne             | Invité                |

| Giraud, Bastien     | Ingénieur Chercheur                     | CEA-LIST                               | Invité                |

---

<sup>a</sup>63<sup>ème</sup> section

UNIVERSITÉ DE LYON

## *Résumé*

École Centrale de Lyon

Institut des Nanotechnologies de Lyon

PhD

**Calcul éco-énergétique avec matériaux ferroélectriques intégrés pour les systèmes embarqués et à la périphérie de réseau**

by Mayeul CANTAN

L'inclusion de matériaux ferroélectriques dans les circuits intégrés suscite de plus en plus d'intérêt, notamment grâce à l'introduction d'oxydes de hafnium dopés au zirconium, compatibles avec les matériaux semi-conducteurs et les procédés de fabrication les plus modernes. Leurs propriétés ferroélectriques, combinées aux technologies **CMOS** conventionnelles, permettent de créer de nouvelles architectures de circuits innovantes. Le rapprochement physique de **Mémoires non volatiles** aux éléments de calcul ouvre de nombreuses possibilités d'amélioration de l'efficacité énergétique en réduisant les transferts de données, en diminuant la consommation d'énergie statique et en permettant l'utilisation de paradigmes de calcul **normalement-éteint** (normally-off computing).

Dans cette thèse, les matériaux ferroélectriques sont abordés du point de vue de la conception de circuits, offrant une explication élémentaire de leurs propriétés et des approches utilisées pour leur modélisation. Plusieurs architectures de circuits utilisant des matériaux ferroélectriques sont également présentées, utilisant des technologies de dépôt en **bout de ligne**, ainsi que de **transistors à effet de champ ferroélectriques (FeFETs, Ferroelectric Field-Effect Transistor)**, avec les résultats de caractérisation électrique obtenus, le cas échéant. Enfin, des techniques d'**exploration de l'espace de conception (DSE, Design-Space Exploration)** et un outil interne d'évaluation des performances au niveau système sont combinés pour extraire des chiffres de performance projetés, afin de permettre une comparaison avec des technologies plus matures, tant au niveau du circuit que du système.

Les résultats obtenus correspondent à la conception de nouveaux circuits, dont certains ont été fabriqués en 130 nm et 28 nm, aux résultats des simulations **DSE** pour des paramètres tels que la fenêtre de mémoire et la consommation d'énergie, ainsi qu'à de multiples outils logiciels créés au long du projet.

## Remerciements

Ce document porte peut-être mon nom sur la première page, mais je n'aurais pas pu le terminer sans les contributions directes et indirectes des personnes qui m'ont aidé et encouragé au long de ce périple. Je ne peux pas lister tout le monde sur cette page, mais à celles et ceux dont le nom n'est pas inscrit : merci pour votre aide et votre soutien tout au long de mon doctorat.

Je suis avant tout reconnaissant à mon directeur de thèse, Ian O'Connor, qui m'a accompagné tout au long de cette thèse, m'apportant soutien et conseils, et se montrant réactif lorsque je rencontrais des difficultés. Mes co-encadrants Cédric Marchand et Damien Deleruyelle ont été d'une grande aide pour discuter des simulations et de la physique des dispositifs ferroélectriques, pour la révision de ce document, ainsi que pour les contributions plus directes de Damien à la [sous-section 2.2.2](#).

Mes remerciements s'étendent à mes estimés collègues et amis pour leur soutien au fil des ans : Clément Zroumba et Arnaud Poittevin m'ont aidé à réaliser le tracé du layout des circuits **MAD200** discutés dans [chapitre 3](#), et ont été source de nombreuses discussions scientifiques fructueuses. Etienne Dupuis, pour sa motivation contagieuse et son cœur sur la main, Adil Brik, Lucien Del Bosque, suivis par les générations suivantes de doctorants, étaient toujours prêts à aider, que ce soit dans le cadre du travail ou pour des questions personnelles. Il en est résulté un environnement de travail accueillant, dans lequel je garde certains de mes meilleurs souvenirs.

Pour leur aide et leur soutien, je voudrais remercier le reste des membres de mon équipe à **INL**, y compris Alberto Bosio, pour son aide avec la synthèse de logique du filtre d'image présenté dans [section 4.6](#). D'autres membres du projet **3εFERRO** ont également été d'une grande aide, y compris à **INL**, où Jordan Bouaziz et d'autres membres de l'équipe Matériaux, notamment Ingrid Cañero Infante, Bertrand Vilquin et Pedro Rojo Romeo, m'ont patiemment enseigné encore et encore les aspects physiques et de fabrication des matériaux ferroélectriques. Je dois également une partie de ma compréhension des matériaux ferroélectriques au personnel de **NaMLab**, en particulier Stefan Slesazeck et Evelyn Breyer, qui ont réalisé une grande partie du travail de conception et de mise en œuvre du filtre d'image convolutif présenté dans la [section 4.6](#). Evelyn a joué un rôle déterminant dans le travail présenté dans ce document en fournissant le modèle de simulation ferroélectrique « Preisach » utilisé pour la plupart des simulations, bien que les premières discussions de modélisation et données expérimentales obtenues m'aient été gracieusement fournies par Carlotta Gastaldi de l'**EPFL**, ce qui a permis mes premières simulations basées sur le modèle « Landau ».

Pour m'avoir successivement aidé à développer la plate-forme d'évaluation des performances au niveau du système décrite dans la [section 5.4](#), je voudrais remercier, dans l'ordre chronologique, les étudiants en master Pierre-Etienne Polet et Luca Mozzone, et le chercheur postdoctoral Marcello Traiolla, pour avoir successivement fourni l'essentiel de l'effort de développement pour la mise en œuvre des architectures que je proposais, et m'avoir fourni d'excellentes critiques à leur sujet. Leurs efforts de documentation ont été extrêmement utiles pour la rédaction de cette section.

Pour leur soutien et leurs encouragements constants, je voudrais également remercier ma famille, y compris mes parents et mes frères et sœurs, qui m'ont constamment taquiné sur l'avancement de mon manuscrit, tout en faisant de leur mieux pour me soutenir pendant ces moments difficiles. L'écriture de ce manuscrit n'a pas été une tâche facile, ni pour moi ni pour les personnes qui m'entourent, c'est pourquoi je suis aussi très reconnaissant envers Liz pour sa patience, sa compréhension et son soutien.

J'ai également trouvé un soutien inconditionnel auprès de mes amis, que je n'ai pas oubliés, et qui me manquent après ce temps passé à travailler de manière isolée. Vous vous reconnaîtrez, et j'espère vous revoir bientôt ! Je tiens à remercier tout particulièrement Claire Segovia pour avoir pris de son temps pour m'aider à travailler sur les premières étapes de la rédaction de ce manuscrit, et pour m'avoir aidée à surmonter le syndrome de la page blanche et à rejeter les distractions, ce qui m'a été extrêmement utile.

De manière moins conventionnelle, j'aimerais également remercier Romano Giannetti, le responsable de la bibliothèque d'illustrations de circuits circuitikz que j'ai largement utilisée tout au long de ce document, pour avoir répondu à ma demande de création de symboles

pour les condensateurs et transistors ferroélectriques<sup>1</sup>. Ces remerciements s'étendent aux mainteneurs des innombrables outils et logiciels libres utilisés au cours de cette thèse, ainsi qu'à Laurent Carrel pour l'administration de nos ressources informatiques locales.

Enfin, je remercie la Commission européenne pour le financement de projets intéressants et pertinents, qui m'a permis de réaliser ce travail dans le cadre du projet **3εFERRO** qui a reçu un financement du programme de recherche et d'innovation Horizon 2020 de l'Union européenne dans le cadre de l'accord de subvention N°780302.

---

<sup>1</sup><https://github.com/circuitikz/circuitikz/issues/515>

# Table des matières

|                                                                                  |           |

|----------------------------------------------------------------------------------|-----------|

| <b>Remerciements</b>                                                             | <b>5</b>  |

| <b>1 Introduction</b>                                                            | <b>17</b> |

| 1.1 À propos de ce document . . . . .                                            | 17        |

| 1.1.1 Licence . . . . .                                                          | 17        |

| 1.1.2 Liens internes et code couleur . . . . .                                   | 18        |

| 1.1.3 Code source du document, errata et matériel supplémentaire . . . . .       | 18        |

| 1.1.4 Objectif du présent document . . . . .                                     | 18        |

| 1.2 Contexte . . . . .                                                           | 18        |

| 1.2.1 Internet des Objets et calcul de périphérie . . . . .                      | 19        |

| Internet des Objets . . . . .                                                    | 19        |

| Calcul de périphérie . . . . .                                                   | 19        |

| 1.2.2 Fin de la mise à l'échelle de Dennard et de la loi de Moore . . . . .      | 20        |

| Loi de Moore . . . . .                                                           | 20        |

| Mise à l'échelle de Dennard . . . . .                                            | 20        |

| Conséquences d'une « mise à l'échelle facile » . . . . .                         | 20        |

| Fin de la mise à l'échelle de Dennard . . . . .                                  | 21        |

| Fin de la loi de Moore . . . . .                                                 | 21        |

| 1.2.3 Architecture Von Neumann . . . . .                                         | 22        |

| 1.2.4 Goulot d'étranglement de Von Neumann . . . . .                             | 22        |

| 1.2.5 HfZrO <sub>2</sub> ferroélectrique . . . . .                               | 23        |

| 1.2.6 Conclusion . . . . .                                                       | 24        |

| 1.3 Projet Européen 3 $\varepsilon$ FERRO . . . . .                              | 24        |

| 1.3.1 Partenaires du projet . . . . .                                            | 24        |

| 1.3.2 Objectifs du projet . . . . .                                              | 25        |

| Accomplissements . . . . .                                                       | 25        |

| Contributions . . . . .                                                          | 25        |

| <b>2 Ferroélectriques : comportement et modélisation</b>                         | <b>27</b> |

| 2.1 Ferroélectricité . . . . .                                                   | 27        |

| 2.1.1 Cristaux ferroélectriques . . . . .                                        | 27        |

| Champ coercif . . . . .                                                          | 28        |

| Polycristaux et domaines . . . . .                                               | 30        |

| Note sur la nomenclature utilisée pour les opérations d'écriture et d'effacement | 31        |

| 2.1.2 Courbe $P$ - $V$ . . . . .                                                 | 31        |

| 2.1.3 Relation avec la capacité et la paraélectricité . . . . .                  | 32        |

| Compensation des charges et champ de dépolarisation . . . . .                    | 34        |

| Jonction à effet Tunnel Ferroélectrique . . . . .                                | 35        |

| 2.1.4 Mesures PUND . . . . .                                                     | 36        |

| 2.2 Modélisation . . . . .                                                       | 38        |

| 2.2.1 Modèle de Landau . . . . .                                                 | 38        |

| Description . . . . .                                                            | 38        |

| Équation . . . . .                                                               | 39        |

| Utilisation . . . . .                                                            | 40        |

| Obtention des paramètres . . . . .                                               | 40        |

| Conclusion . . . . .                                                             | 41        |

| 2.2.2 Modèle de Preisach . . . . .                                               | 41        |

| Remerciements . . . . .                                                          | 41        |

| Hystérons . . . . .                                                              | 41        |

|                                                                                       |           |

|---------------------------------------------------------------------------------------|-----------|

| Comportement cumulatif des hystérons . . . . .                                        | 44        |

| Limites . . . . .                                                                     | 44        |

| 2.2.3 Modèle simplifié pour les simulations à grande échelle . . . . .                | 47        |

| 2.3 Condensateurs ferroélectriques . . . . .                                          | 48        |

| 2.3.1 Condensateur ordinaire . . . . .                                                | 48        |

| 2.3.2 Non-volatilité . . . . .                                                        | 48        |

| 2.3.3 Capacité négative . . . . .                                                     | 49        |

| 2.4 Transistors ferroélectriques . . . . .                                            | 50        |

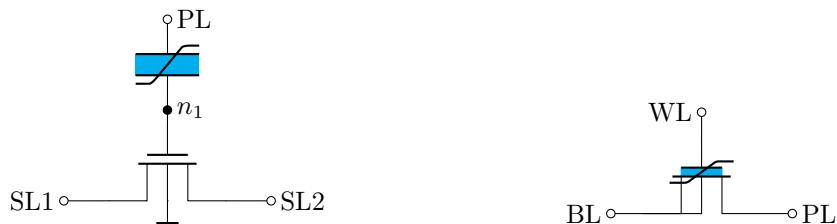

| 2.4.1 Dispositifs FeFET . . . . .                                                     | 50        |

| Désavantages . . . . .                                                                | 50        |

| 2.4.2 Empilements de grille . . . . .                                                 | 51        |

| 2.4.3 Modélisation . . . . .                                                          | 52        |

| 2.5 État de l'art des circuits ferroélectriques . . . . .                             | 52        |

| 2.5.1 Hafnium ferroélectrique . . . . .                                               | 52        |

| Modélisation . . . . .                                                                | 52        |

| 2.5.2 Conception de circuits Condensateur Ferroélectriques et bout de ligne . . . . . | 53        |

| 2.5.3 Circuits utilisant des transistors à effet de champ ferroélectriques . . . . .  | 53        |

| Transistors à effet de champ ferroélectriques canal P . . . . .                       | 53        |

| 2.5.4 Comparaison avec d'autres Mémoires non volatiles . . . . .                      | 54        |

| 2.5.5 Exploration de l'espace de conception . . . . .                                 | 54        |

| 2.5.6 Évaluation des performances au niveau du système . . . . .                      | 56        |

| Prototypage matériel . . . . .                                                        | 57        |

| Émulateurs FPGA . . . . .                                                             | 57        |

| Simulateurs logiciels . . . . .                                                       | 57        |

| Prise en charge par les compilateurs et instrumentation du code . . . . .             | 57        |

| <b>3 Circuits à condensateurs ferroélectriques</b>                                    | <b>59</b> |

| 3.1 Introduction . . . . .                                                            | 59        |

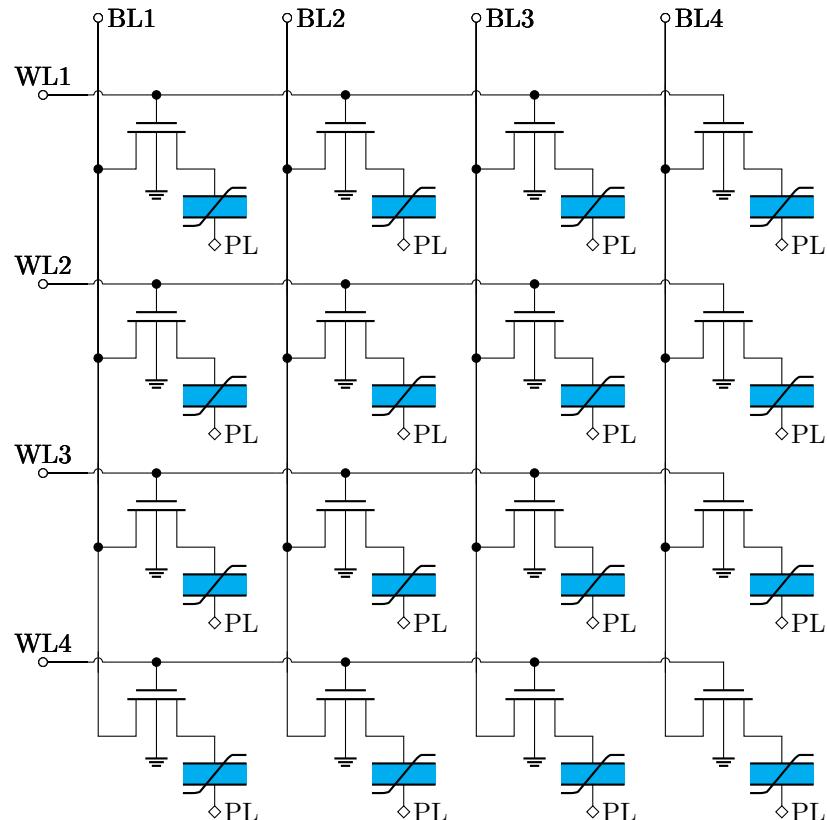

| 3.1.1 Technologie bout de ligne . . . . .                                             | 59        |

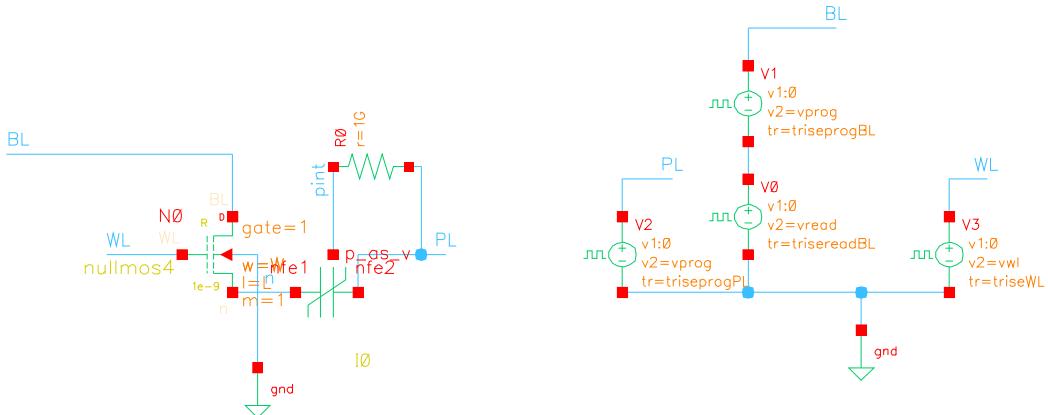

| 3.1.2 Technologie MAD200 . . . . .                                                    | 60        |

| 3.2 Cellule de mémoire 1T1C . . . . .                                                 | 61        |

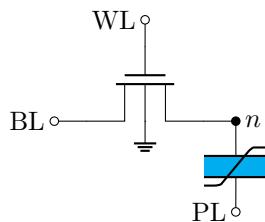

| 3.2.1 Opération . . . . .                                                             | 61        |

| Sélection et programmation des cellules mémoire . . . . .                             | 61        |

| Lecture de la cellule mémoire . . . . .                                               | 62        |

| Mémoire à plusieurs niveaux . . . . .                                                 | 63        |

| 3.2.2 Simulation . . . . .                                                            | 64        |

| Simulations en technologie MAD200 . . . . .                                           | 64        |

| 3.3 Structure de type FeFET . . . . .                                                 | 64        |

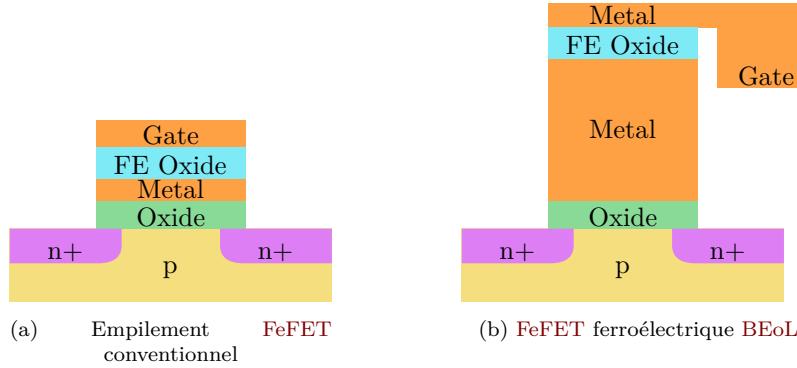

| 3.3.1 Description . . . . .                                                           | 64        |

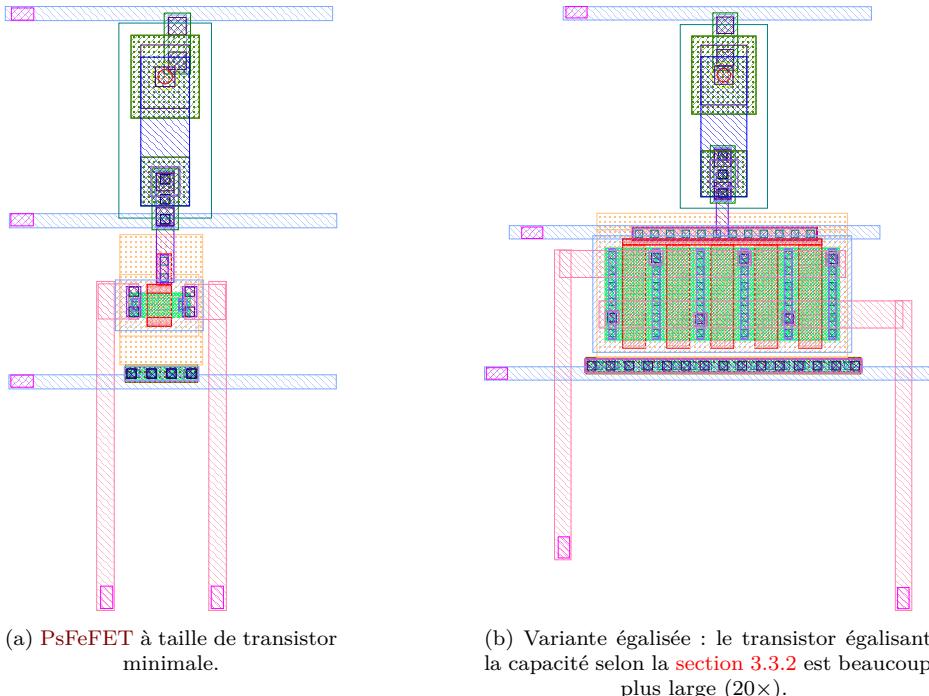

| 3.3.2 Conception . . . . .                                                            | 66        |

| Égalisation de la capacité . . . . .                                                  | 66        |

| 3.3.3 Caractérisation . . . . .                                                       | 68        |

| Protocole et résultats . . . . .                                                      | 68        |

| 3.3.4 Extension aux circuits à transistors multiples . . . . .                        | 70        |

| 3.4 TCAM à lecture destructive . . . . .                                              | 72        |

| 3.4.1 Description . . . . .                                                           | 72        |

| mémoire ternaire adressable par contenu . . . . .                                     | 72        |

| Principe de fonctionnement . . . . .                                                  | 72        |

| Limites . . . . .                                                                     | 73        |

| 3.4.2 Conception . . . . .                                                            | 75        |

| 3.5 Bitcell polyvalente 2T1C . . . . .                                                | 77        |

| 3.5.1 Description . . . . .                                                           | 77        |

| Programmation . . . . .                                                               | 77        |

| Lecture FTJ – Lecture non destructrice . . . . .                                      | 78        |

| Lecture en mode DRAM, ou 1T1C – Lecture destructrice . . . . .                        | 78        |

| Lecture en mode FeFET – Lecture non destructive . . . . .                             | 78        |

| 2T-nC . . . . .                                                                       | 79        |

| Émulation de la TCAM destructrice . . . . .                                           | 80        |

|          |                                                                                            |           |

|----------|--------------------------------------------------------------------------------------------|-----------|

| 3.5.2    | Conception . . . . .                                                                       | 80        |

|          | Égalisation de la capacité pour le fonctionnement DRAM avec lecture destructrice . . . . . | 80        |

|          | 2T-nC . . . . .                                                                            | 80        |

| 3.5.3    | Résultats de caractérisation . . . . .                                                     | 82        |

|          | Tracé $I_{DS}$ — $V_{GS}$ de référence pour $Q_R$ . . . . .                                | 82        |

|          | Protocole de caractérisation . . . . .                                                     | 83        |

|          | Résultats et interprétation . . . . .                                                      | 83        |

|          | Enquête sur la dynamique de commutation . . . . .                                          | 84        |

| 3.6      | Conclusion . . . . .                                                                       | 85        |

| 3.6.1    | Cellule de mémoire 1T1C . . . . .                                                          | 85        |

| 3.6.2    | Structure FeFET bout de ligne . . . . .                                                    | 85        |

| 3.6.3    | TCAM à lecture destructive . . . . .                                                       | 85        |

| 3.6.4    | 2T1C . . . . .                                                                             | 86        |

| <b>4</b> | <b>Circuits à transistors ferroélectriques</b>                                             | <b>87</b> |

| 4.1      | Introduction aux circuits FeFET . . . . .                                                  | 87        |

| 4.1.1    | Programmation de l'oxyde ferroélectrique . . . . .                                         | 88        |

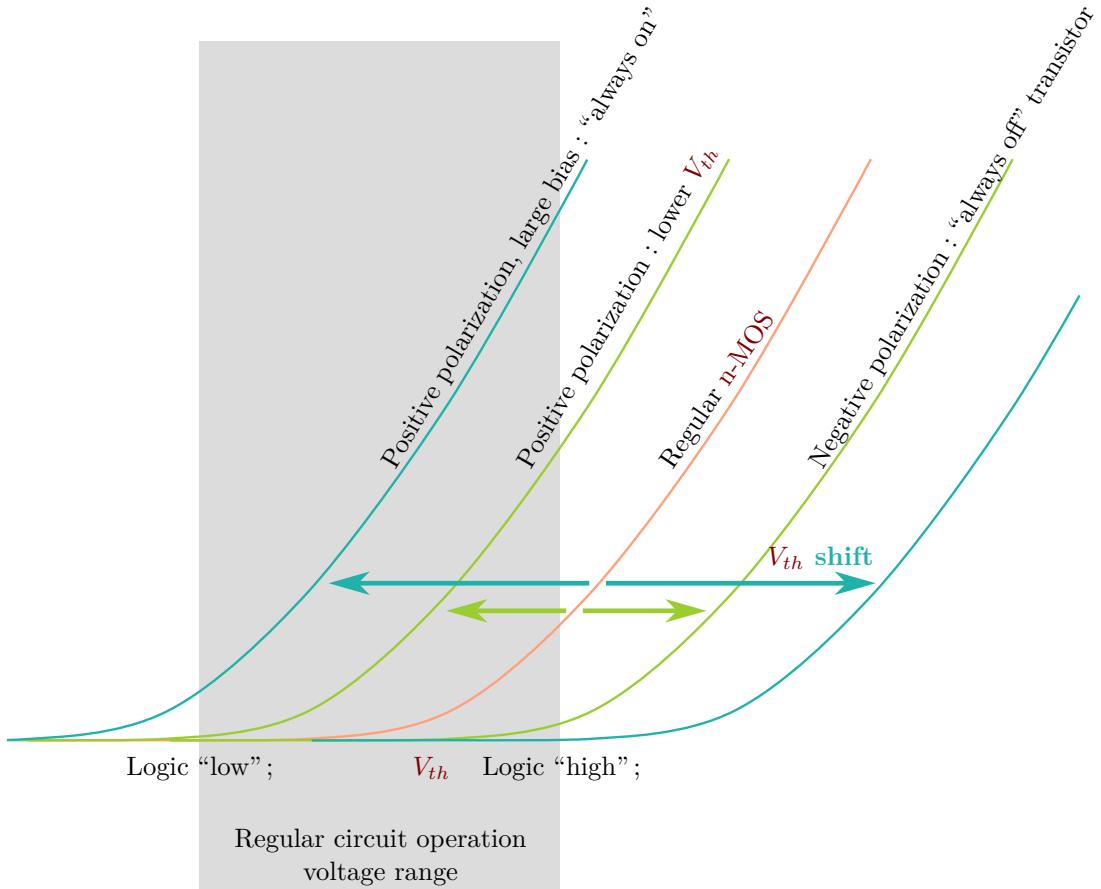

| 4.1.2    | Décalage du $V_{th}$ . . . . .                                                             | 88        |

|          | Contrôle analogique du décalage de $V_{th}$ . . . . .                                      | 88        |

|          | Décalage de $V_{th}$ entre deux positions . . . . .                                        | 90        |

| 4.1.3    | Comparaison avec la logique CMOS . . . . .                                                 | 90        |

|          | Avantages par rapport à la logique CMOS . . . . .                                          | 90        |

|          | Inconvénients par rapport à la logique CMOS . . . . .                                      | 91        |

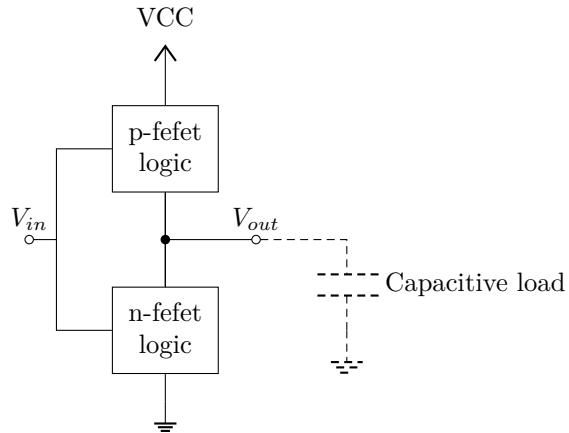

|          | Procédé technologique et disponibilité de p-FeFET . . . . .                                | 91        |

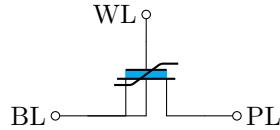

| 4.2      | Mémoire 1T-FeFET . . . . .                                                                 | 91        |

| 4.2.1    | Principe de fonctionnement . . . . .                                                       | 91        |

|          | Opération de lecture . . . . .                                                             | 92        |

|          | Opération d'écriture . . . . .                                                             | 93        |

| 4.2.2    | Comparaison avec technologies de mémoires à transistors à grille flottante . . . . .       | 93        |

| 4.2.3    | Mode de fonctionnement hybride . . . . .                                                   | 93        |

| 4.3      | Circuits de transrésistance . . . . .                                                      | 94        |

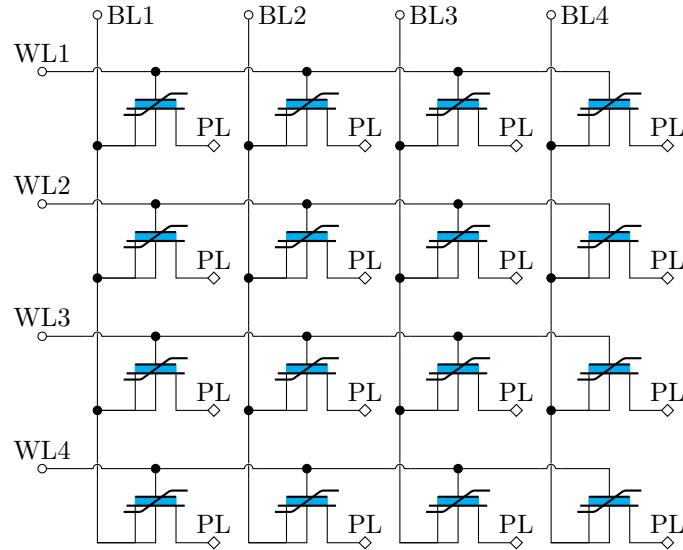

| 4.3.1    | Logique complémentaire avec p-FeFET . . . . .                                              | 94        |

| 4.3.2    | Logique résistive . . . . .                                                                | 96        |

| 4.3.3    | Logique dynamique . . . . .                                                                | 96        |

|          | Logique dynamique hybride avec étage CMOS . . . . .                                        | 96        |

| 4.3.4    | Logique à transistors ballast . . . . .                                                    | 98        |

|          | Transistors ballast à FeFET . . . . .                                                      | 98        |

| 4.4      | Portes logiques non volatiles à FeFET . . . . .                                            | 98        |

| 4.4.1    | NV-NAND2 . . . . .                                                                         | 99        |

| 4.4.2    | NV-AND2 . . . . .                                                                          | 99        |

| 4.4.3    | NV-XOR2 . . . . .                                                                          | 99        |

| 4.5      | FeFETs comme technologie d'appoint . . . . .                                               | 100       |

| 4.5.1    | Cellule mémoire Black & Das comme mécanisme de checkpointing . . . . .                     | 100       |

| 4.6      | Filtre d'image convolutif avec logique en mémoire FeFET . . . . .                          | 102       |

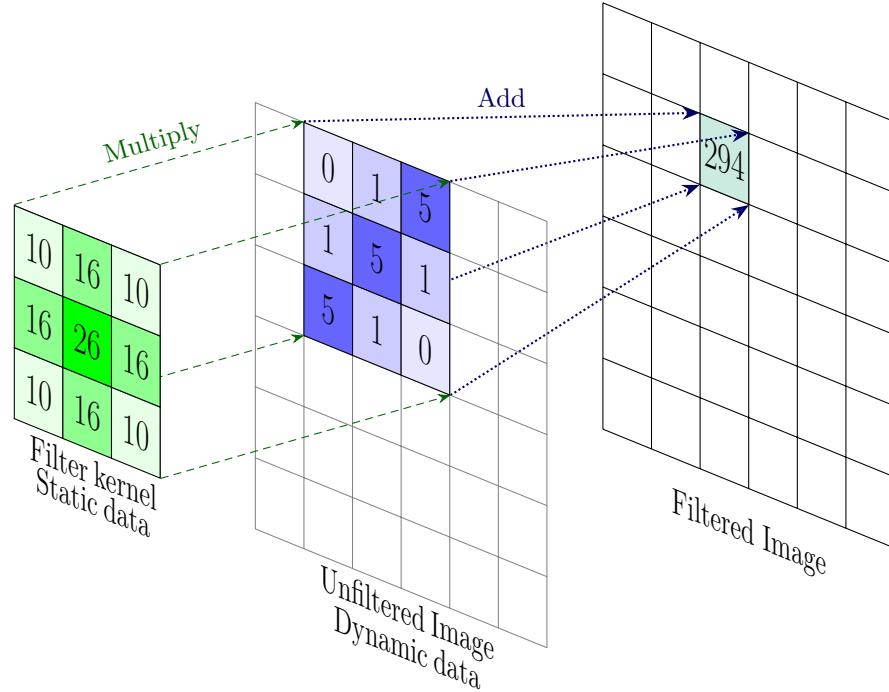

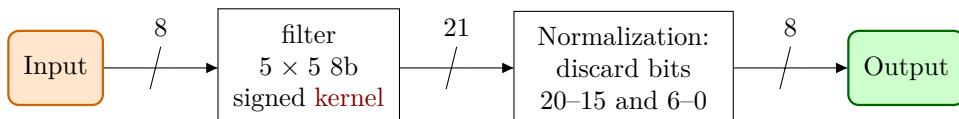

| 4.6.1    | Choix d'un filtre d'image convolutif . . . . .                                             | 102       |

|          | Opération de convolution à une dimension . . . . .                                         | 103       |

|          | Convolution d'une image bidimensionnelle . . . . .                                         | 103       |

|          | Post-traitement nécessaire . . . . .                                                       | 104       |

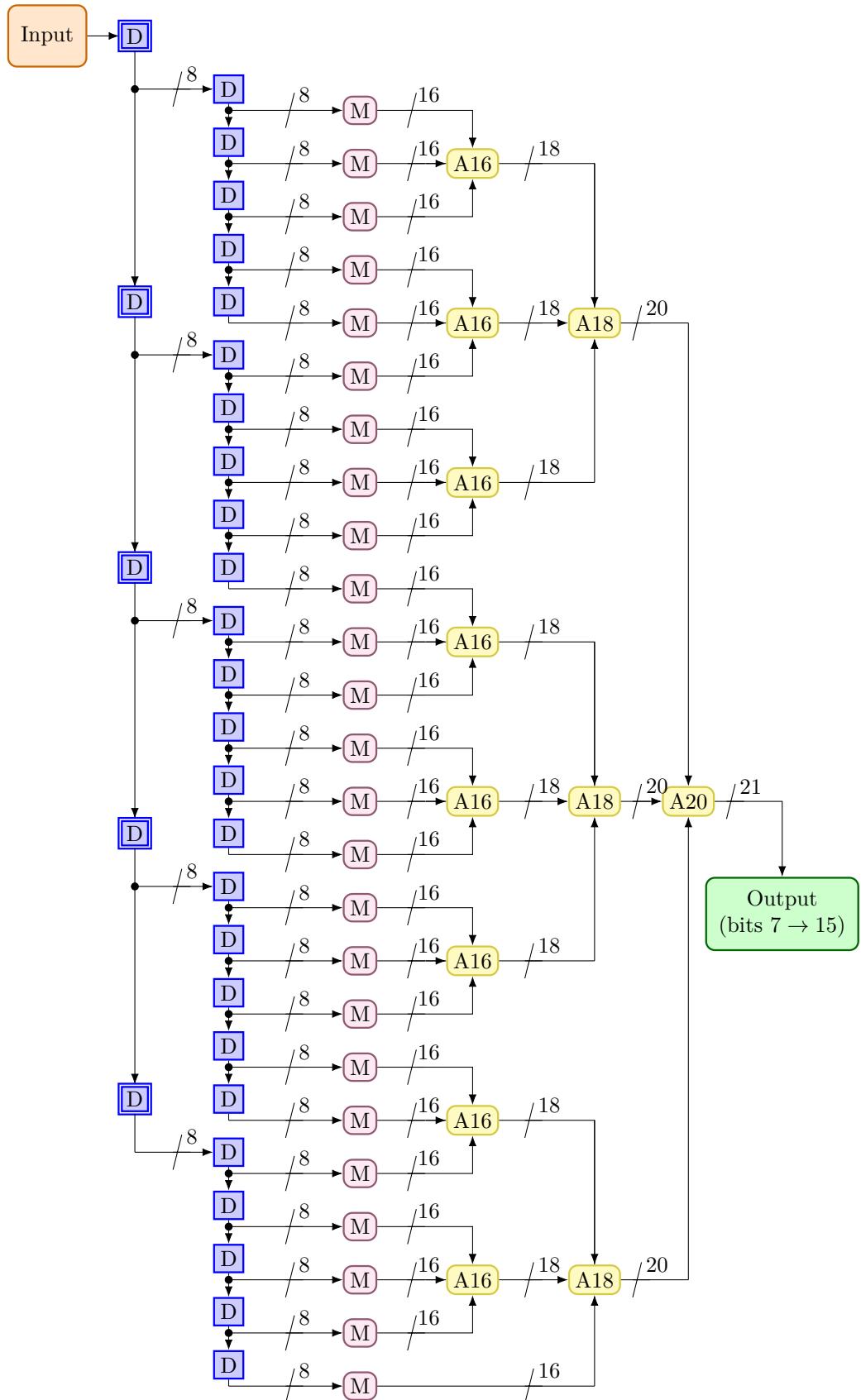

| 4.6.2    | Architecture du filtre . . . . .                                                           | 105       |

|          | Échantillons intermédiaires . . . . .                                                      | 105       |

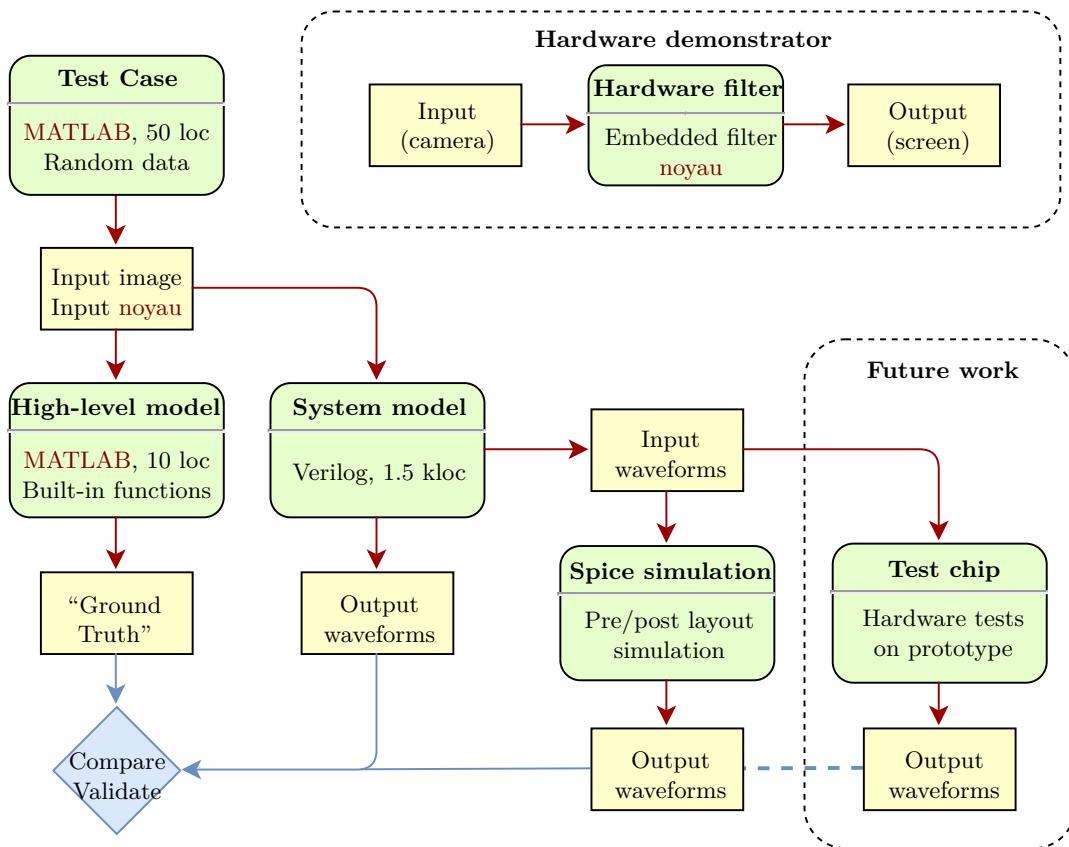

|          | Chaîne de test . . . . .                                                                   | 105       |

|          | Précision binaire . . . . .                                                                | 107       |

| 4.6.3    | Multiplicateur logique en mémoire à FeFET . . . . .                                        | 108       |

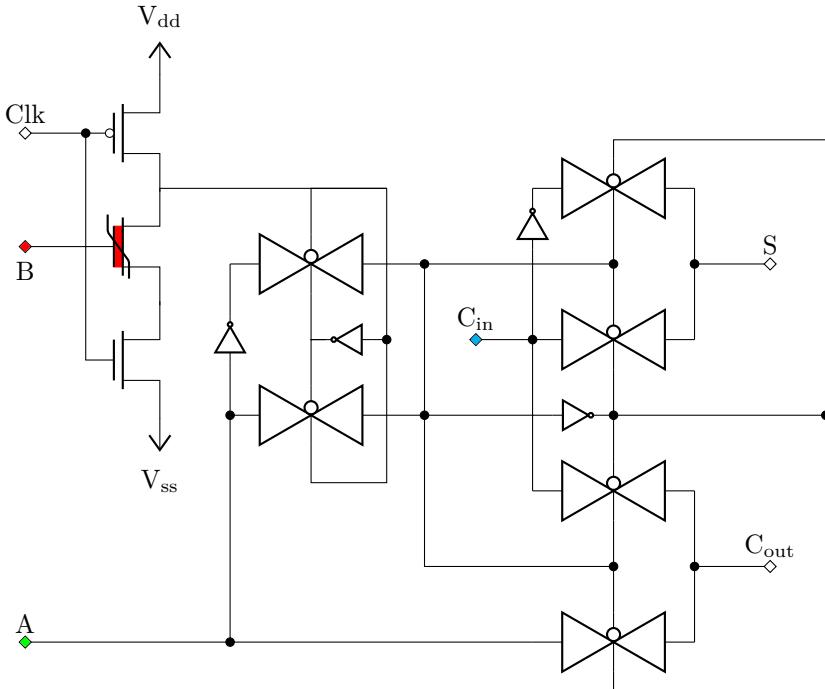

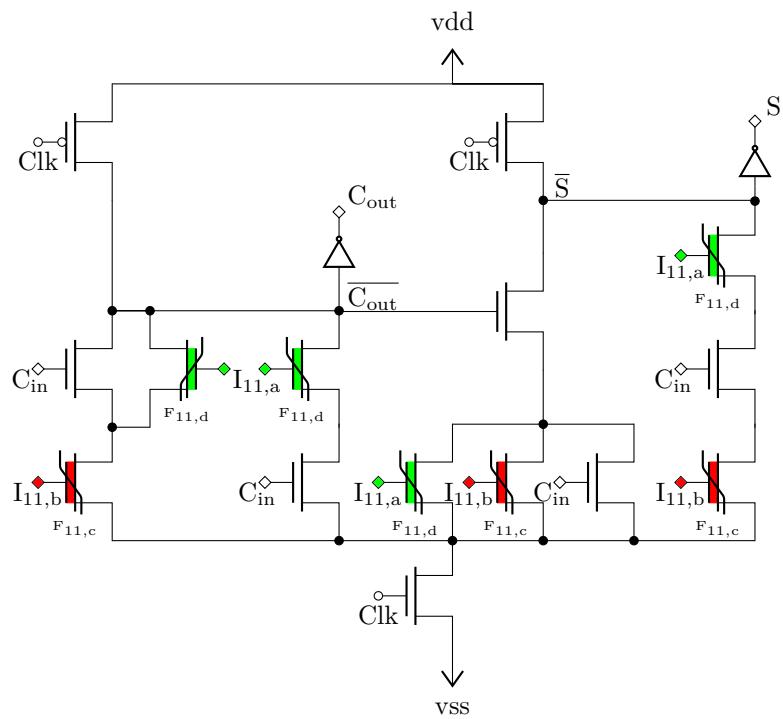

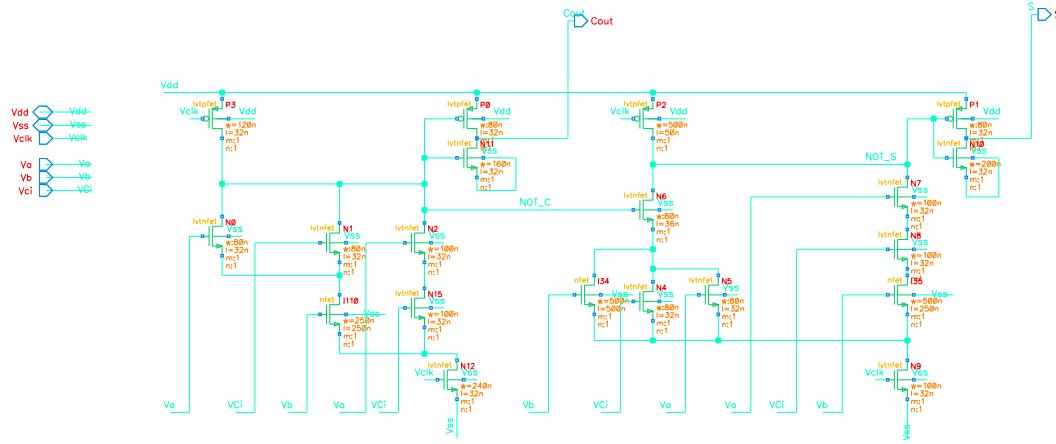

|          | Circuit multiplicateur et circuit additionneur . . . . .                                   | 108       |

|          | Additionneur à propagation de retenue . . . . .                                            | 108       |

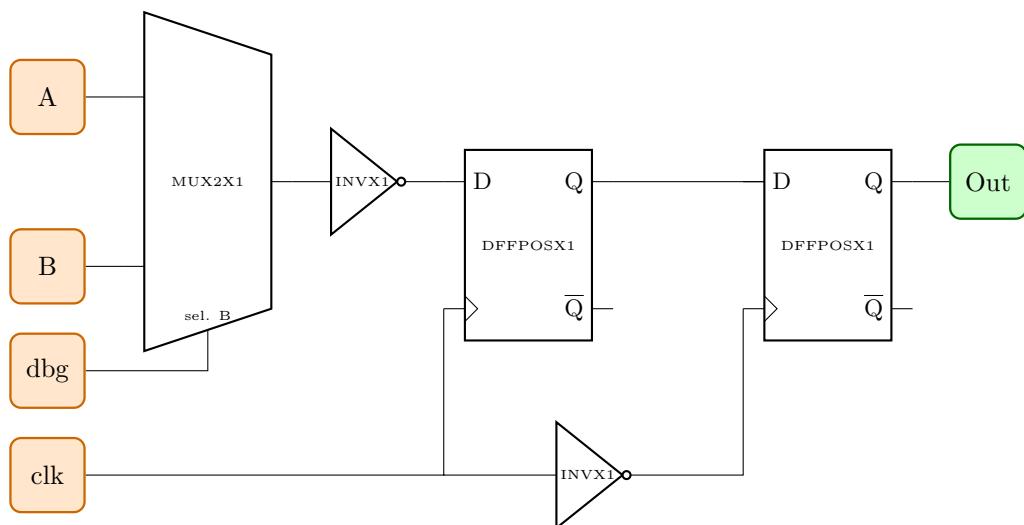

|          | Architecture pipelinée . . . . .                                                           | 108       |

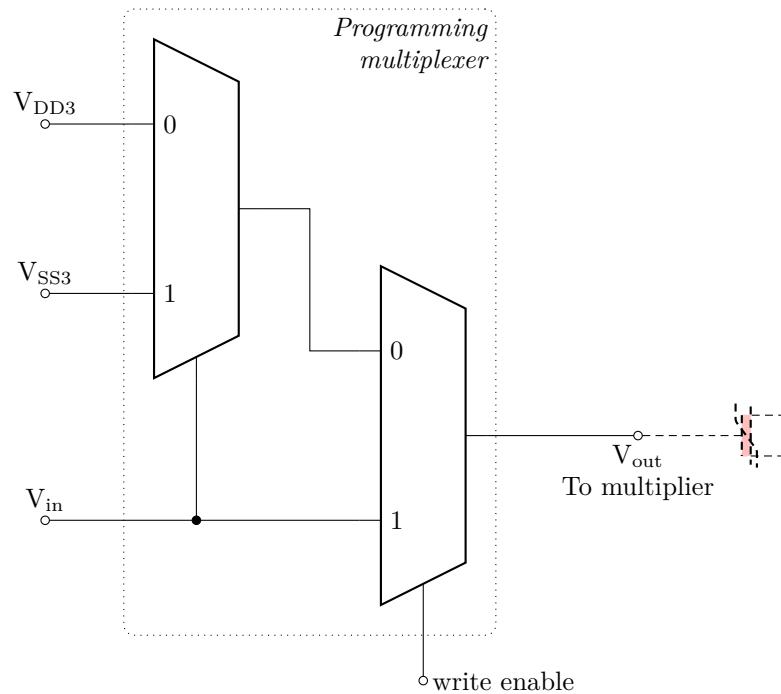

|          | Programmation des coefficients poids du noyau . . . . .                                    | 112       |

|          |                                                                               |                                                    |     |

|----------|-------------------------------------------------------------------------------|----------------------------------------------------|-----|

| 4.6.4    | Validation en simulation et problèmes identifiés . . . . .                    | 112                                                |     |

|          | Simplification de la simulation au niveau circuit . . . . .                   | 114                                                |     |

|          | Génération de signaux d'entrée et de sortie de référence . . . . .            | 114                                                |     |

|          | Mauvaise synchronisation pour déclencher le multiplicateur . . . . .          | 115                                                |     |

|          | Signaux dépendant de la décharge du nœud flottant . . . . .                   | 116                                                |     |

| 4.6.5    | Résultats . . . . .                                                           | 117                                                |     |

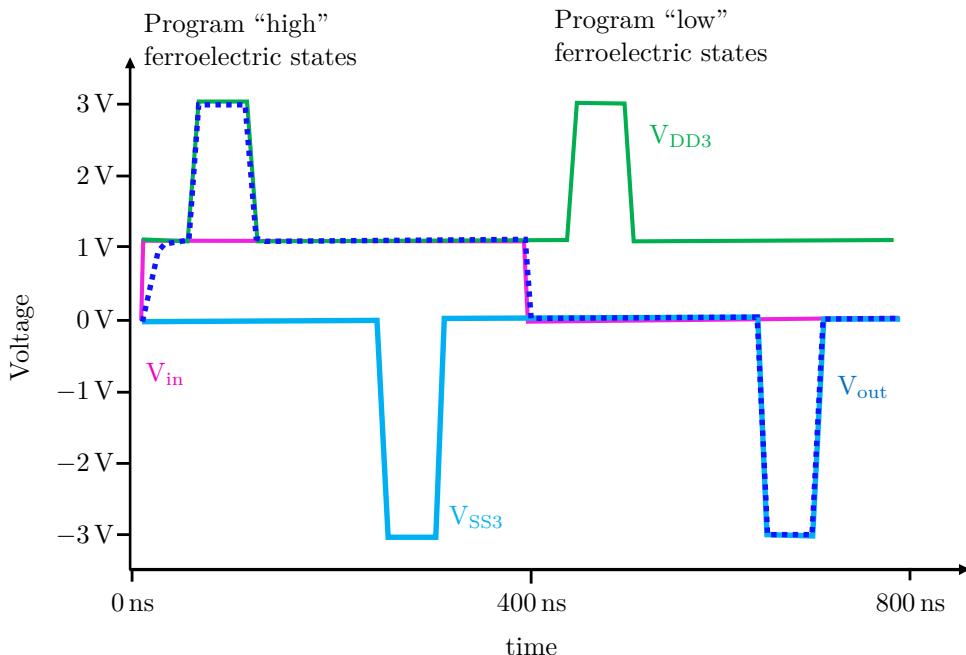

|          | Programmation des coefficients . . . . .                                      | 117                                                |     |

|          | Point de fonctionnement . . . . .                                             | 117                                                |     |

|          | Démonstrateur interactif final . . . . .                                      | 119                                                |     |

| 4.7      | Conclusion . . . . .                                                          | 121                                                |     |

| 4.7.1    | Logique à FeFET . . . . .                                                     | 121                                                |     |

| 4.7.2    | Filtre d'image . . . . .                                                      | 121                                                |     |

| 4.7.3    | Mémoires à FeFET . . . . .                                                    | 122                                                |     |

| <b>5</b> | <b>Exploration et optimisation de l'espace de conception</b>                  | <b>123</b>                                         |     |

| 5.1      | Introduction à l'exploration d'espace de conception . . . . .                 | 124                                                |     |

| 5.1.1    | Espace des paramètres et espace des performances, optimal de Pareto . . . . . | 124                                                |     |

|          | Espace de paramètres et de performance . . . . .                              | 124                                                |     |

|          | Optimisation multi-objectifs . . . . .                                        | 125                                                |     |

|          | Front de Pareto . . . . .                                                     | 125                                                |     |

| 5.1.2    | Exploration automatisée . . . . .                                             | 126                                                |     |

|          | Procédure . . . . .                                                           | 126                                                |     |

|          | 5.1.3                                                                         | Étude des performances au niveau système . . . . . | 127 |

| 5.2      | Outils d'exploration de l'espace de conception . . . . .                      | 127                                                |     |

| 5.2.1    | Optimiseur LIFT . . . . .                                                     | 127                                                |     |

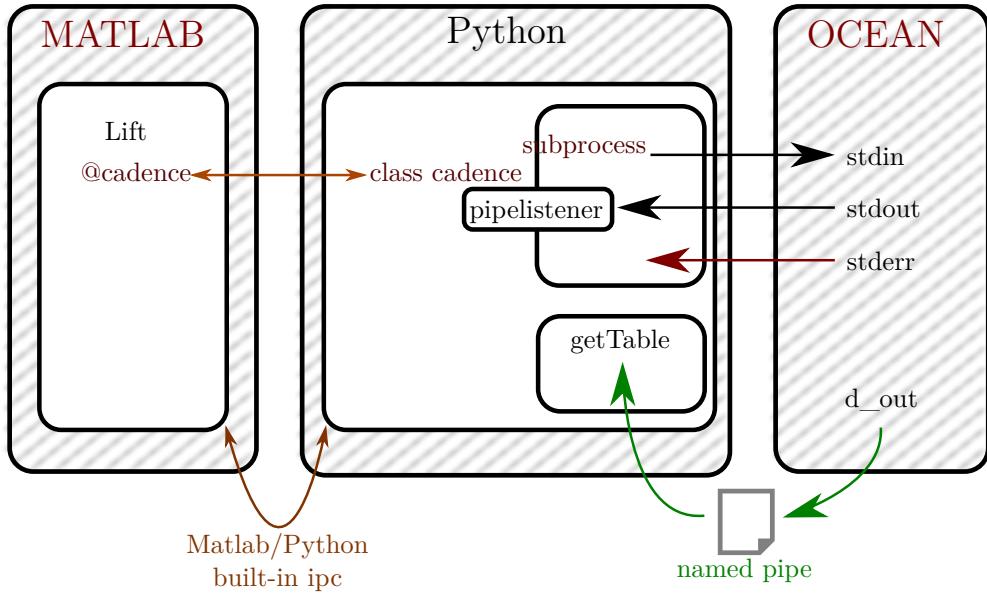

| 5.2.2    | IPC Cadence . . . . .                                                         | 128                                                |     |

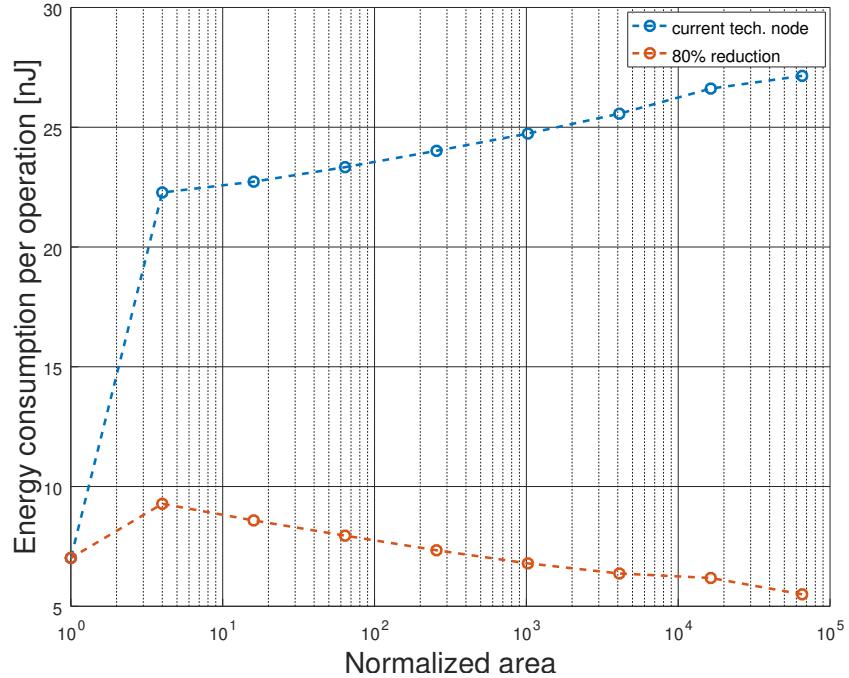

| 5.3      | Résultats de l'exploration de l'espace de conception . . . . .                | 128                                                |     |

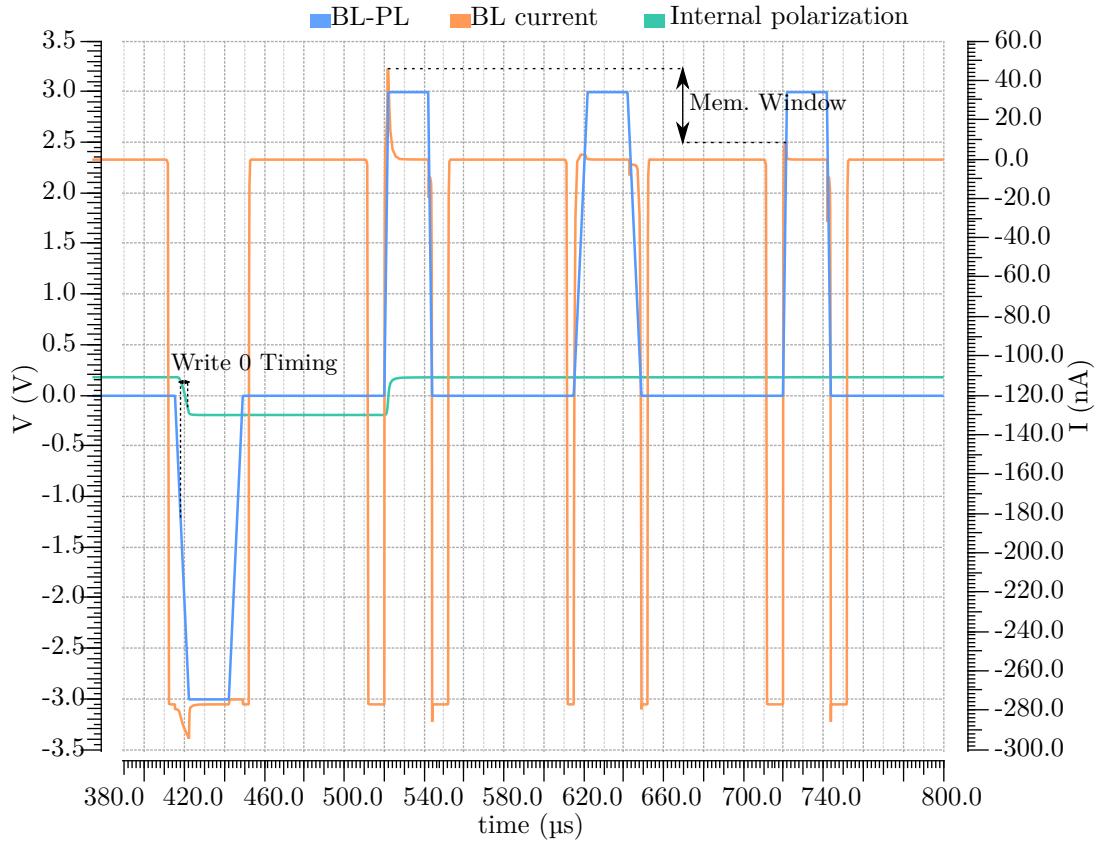

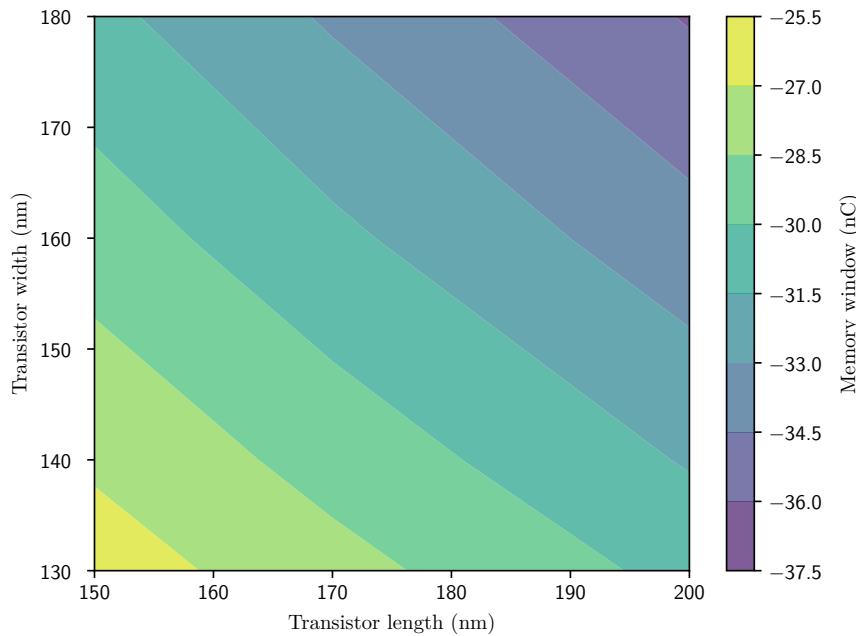

| 5.3.1    | Échantillonnage de l'espace de conception de la bitcell 1T1C . . . . .        | 129                                                |     |

|          | Description du problème et résultats attendus . . . . .                       | 129                                                |     |

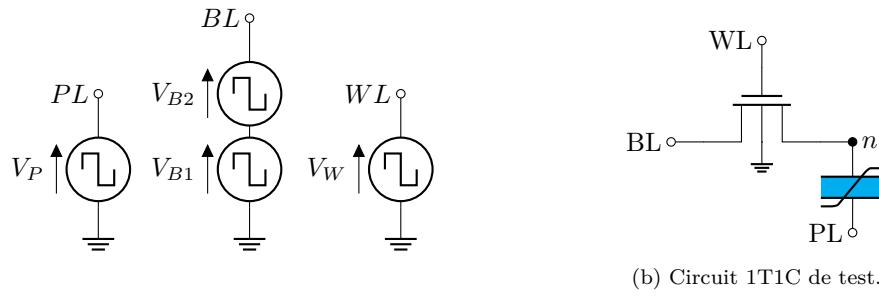

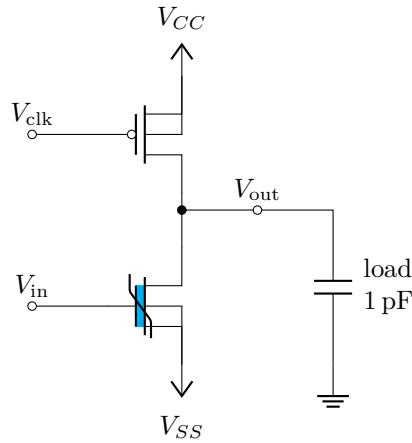

|          | Circuit de test . . . . .                                                     | 130                                                |     |

|          | Définition du problème . . . . .                                              | 131                                                |     |

|          | Extraction des métriques . . . . .                                            | 132                                                |     |

|          | Résultats . . . . .                                                           | 132                                                |     |

| 5.3.2    | Porte logique non volatile NAND à FeFET (NV-NAND2) . . . . .                  | 134                                                |     |

|          | Circuit de test et espace de paramètres . . . . .                             | 134                                                |     |

|          | Espace de performance . . . . .                                               | 138                                                |     |

|          | Résultats . . . . .                                                           | 138                                                |     |

| 5.4      | Plate-forme d'analyse des performances au niveau système . . . . .            | 140                                                |     |

| 5.4.1    | Introduction . . . . .                                                        | 140                                                |     |

|          | Objectifs . . . . .                                                           | 140                                                |     |

|          | Cas d'utilisation . . . . .                                                   | 140                                                |     |

|          | Remerciements . . . . .                                                       | 140                                                |     |

| 5.4.2    | Champ d'application de la plateforme d'évaluation des performances . . . . .  | 140                                                |     |

|          | Architectures système cibles . . . . .                                        | 140                                                |     |

|          | Métriques extraites . . . . .                                                 | 140                                                |     |

|          | Algorithmes de test . . . . .                                                 | 141                                                |     |

| 5.4.3    | Mise en œuvre . . . . .                                                       | 141                                                |     |

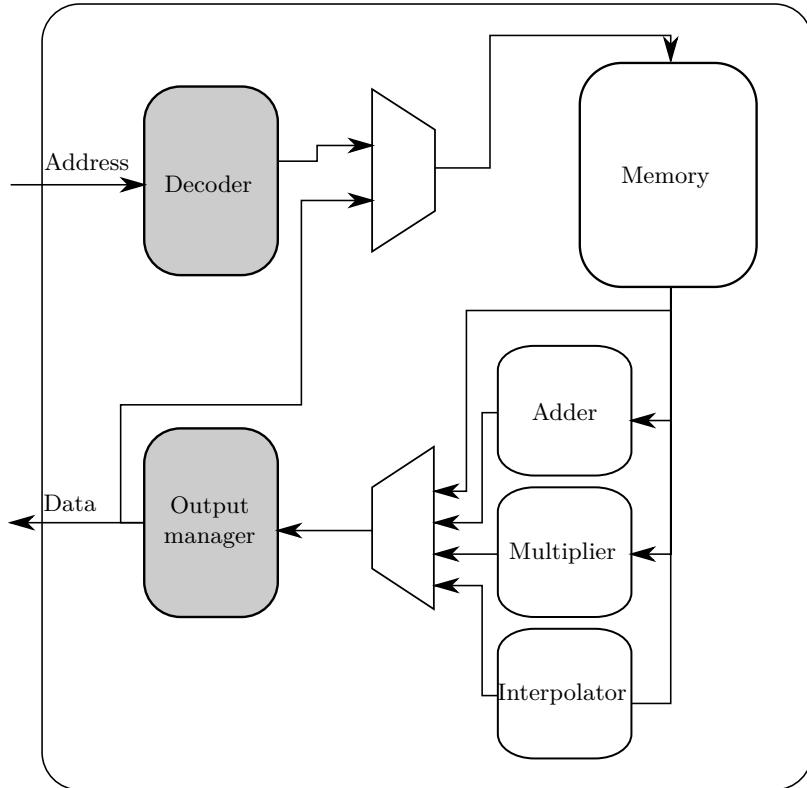

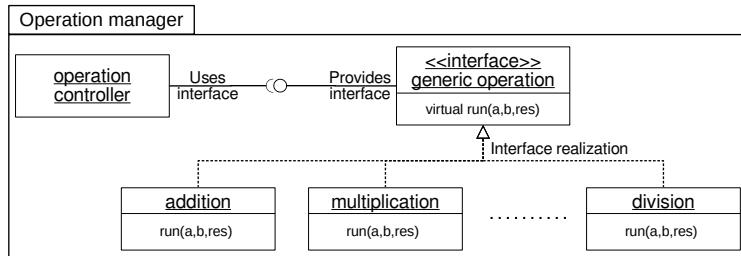

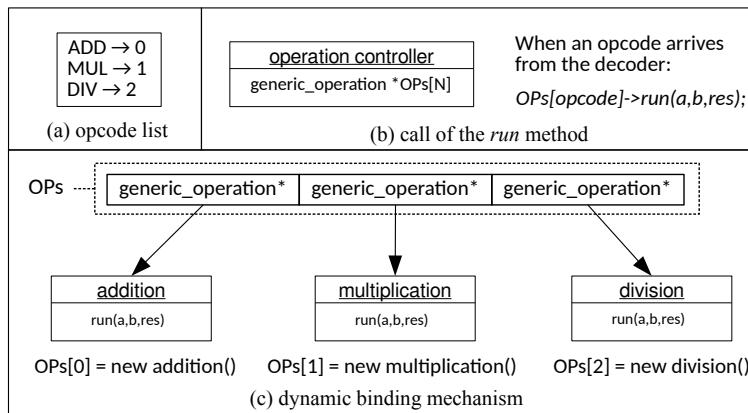

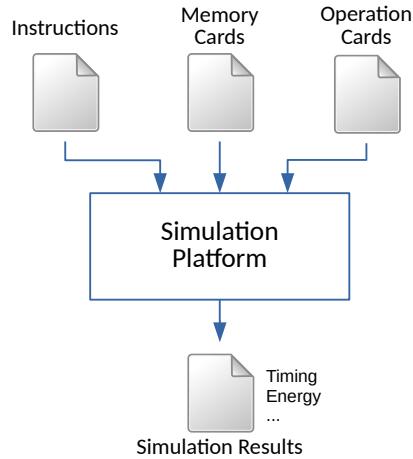

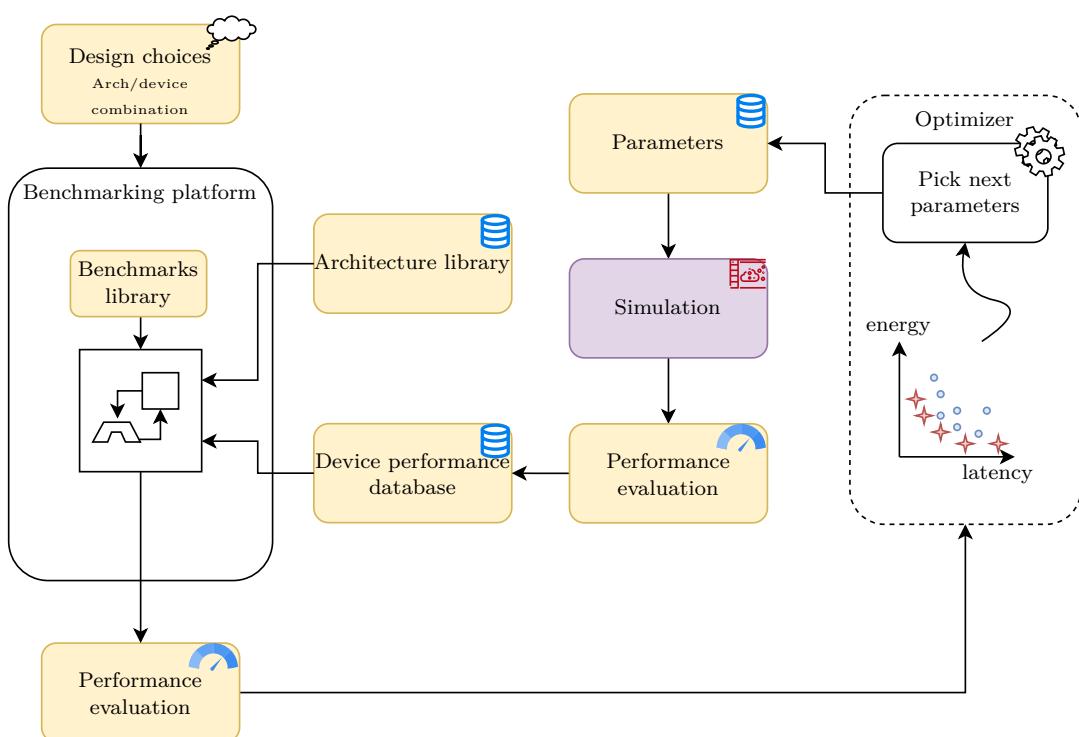

|          | Architecture . . . . .                                                        | 142                                                |     |

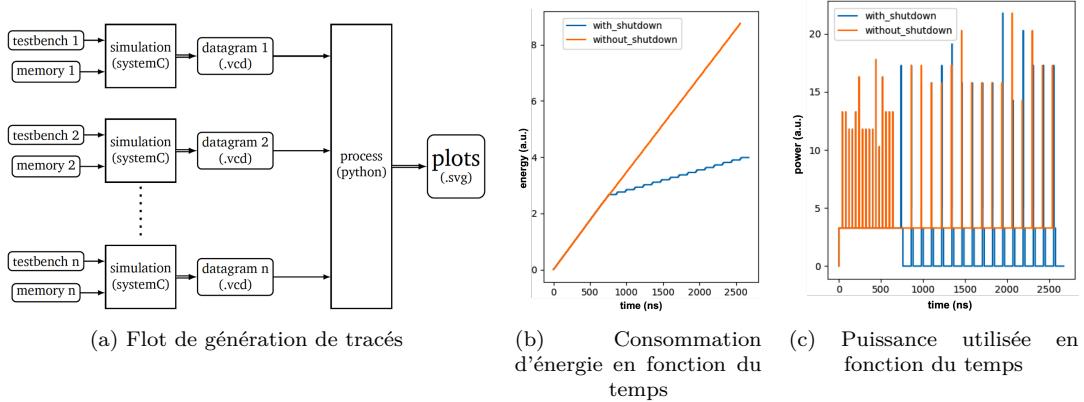

|          | Pipeline de simulation . . . . .                                              | 143                                                |     |

|          | Module de contrôle décodeur . . . . .                                         | 143                                                |     |

|          | Module de gestion de la sortie . . . . .                                      | 143                                                |     |

|          | Calcul et suivi des performances . . . . .                                    | 144                                                |     |

| 5.4.4    | Modules opérationnels et cartes modèles . . . . .                             | 144                                                |     |

|          | Module mémoire . . . . .                                                      | 144                                                |     |

|          | Modules opérationnels . . . . .                                               | 144                                                |     |

|          | Implémentation des modules opérationnels . . . . .                            | 145                                                |     |

|          | Structure de la carte modèle . . . . .                                        | 145                                                |     |

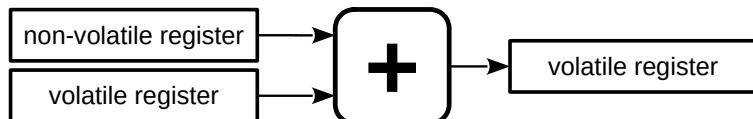

| 5.4.5    | Exemple pratique : Additionneur . . . . .                                     | 146                                                |     |

|                                |                                                                         |            |

|--------------------------------|-------------------------------------------------------------------------|------------|

| 5.5                            | Résultats de l'exploration au niveau système . . . . .                  | 147        |

| 5.5.1                          | Cas d'utilisation normalement-éteint . . . . .                          | 148        |

| 5.5.2                          | Simulations de circuit interpolateur . . . . .                          | 148        |

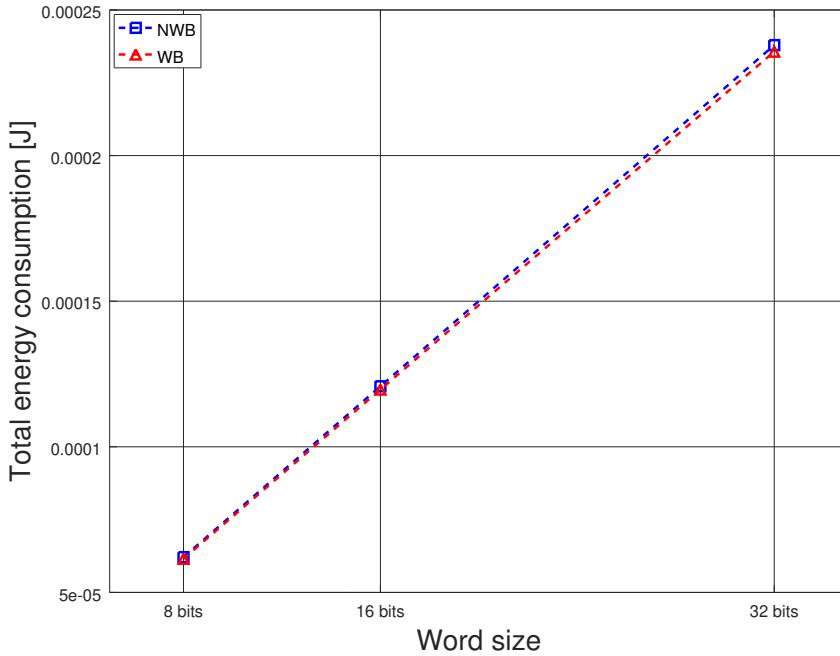

| 5.5.3                          | Mesure de performance sur multiplication matricielle . . . . .          | 150        |

| 5.6                            | Conclusion . . . . .                                                    | 150        |

| 5.6.1                          | Exploration de l'espace de conception . . . . .                         | 150        |

|                                | Instabilité des modèles et précision . . . . .                          | 151        |

| 5.6.2                          | Plate-forme d'évaluation des performances au niveau système . . . . .   | 152        |

|                                | Statut actuel . . . . .                                                 | 152        |

|                                | Approfondissement et analyses complémentaires . . . . .                 | 152        |

|                                | Co-optimisation circuit et technologie . . . . .                        | 152        |

| <b>6</b>                       | <b>Conclusion</b>                                                       | <b>155</b> |

| 6.1                            | Technologie ferroélectrique bout de ligne . . . . .                     | 155        |

| 6.2                            | Avantages et limitations actuelles des FeFETs . . . . .                 | 155        |

| 6.2.1                          | Avenir de la technologie FeFET . . . . .                                | 156        |

| 6.3                            | DSE automatisée et modélisation . . . . .                               | 156        |

| 6.3.1                          | Problèmes de modélisation . . . . .                                     | 156        |

| 6.4                            | Évaluation des performances au niveau du système . . . . .              | 157        |

| 6.5                            | Perspectives à court terme . . . . .                                    | 157        |

| 6.5.1                          | Travaux de caractérisation restants . . . . .                           | 157        |

| 6.5.2                          | Simulations futures . . . . .                                           | 157        |

| 6.6                            | Considérations sur l'avenir de la technologie ferroélectrique . . . . . | 158        |

| 6.6.1                          | Compacité . . . . .                                                     | 158        |

| 6.6.2                          | Signaux de contrôle . . . . .                                           | 158        |

| <b>Bibliographie</b>           | <b>161</b>                                                              |            |

| <b>Glossary</b>                | <b>173</b>                                                              |            |

| <b>Acronyms</b>                | <b>177</b>                                                              |            |

| <b>A Extraits de code</b>      | <b>179</b>                                                              |            |

| <b>B Circuits additionnels</b> | <b>195</b>                                                              |            |

| <b>C Tableaux additionnels</b> | <b>197</b>                                                              |            |

# Table des figures

|      |                                                                                               |     |

|------|-----------------------------------------------------------------------------------------------|-----|

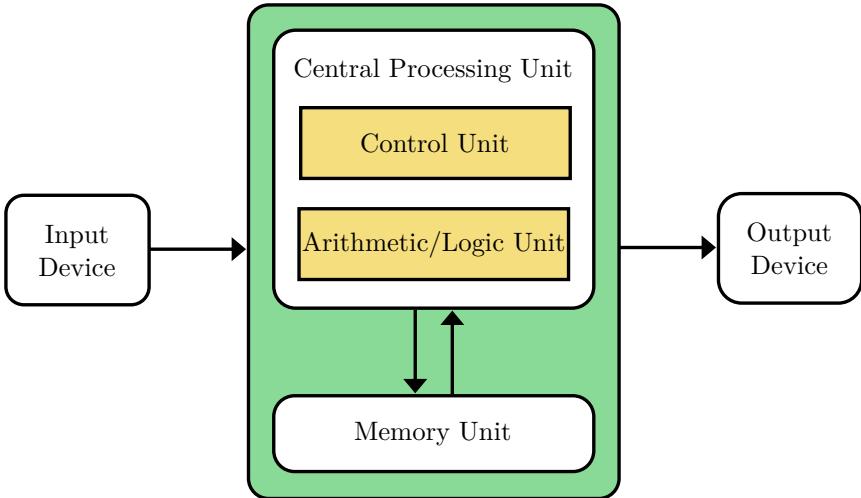

| 1.1  | Diagramme de l'architecture Von Neumann . . . . .                                             | 23  |

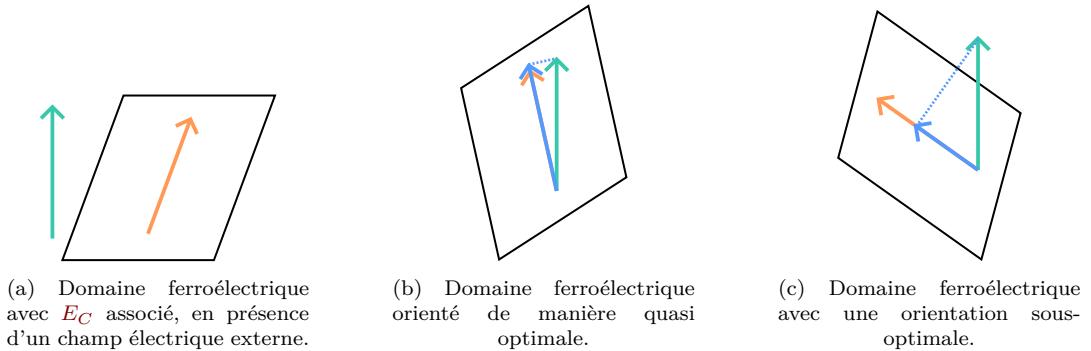

| 2.1  | Effet du décalage d'orientation entre les domaines et le champ électrique externe. . . . .    | 29  |

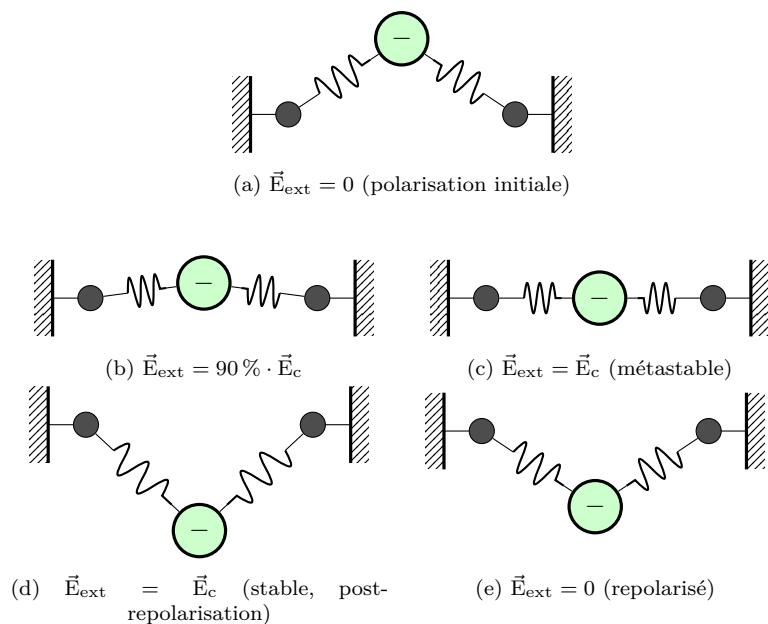

| 2.2  | Illustration de la ferroélectricité avec un système charge-ressort équivalent. . . . .        | 29  |

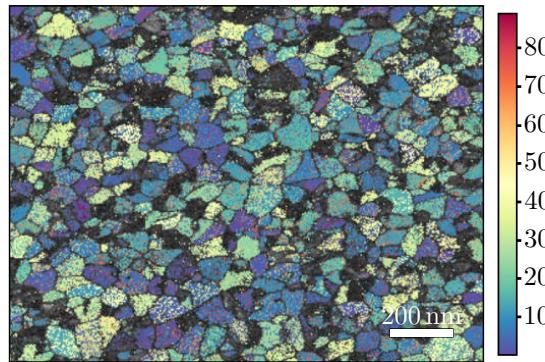

| 2.3  | Mesure expérimentale de l'orientation des domaines dans HfO <sub>2</sub> dopé en Si . . . . . | 30  |

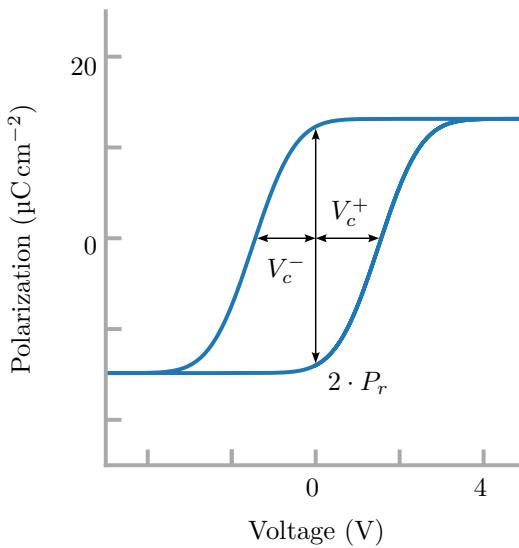

| 2.4  | Lecture de Pr et $V_C$ sur une courbe $P$ - $V$ . . . . .                                     | 32  |

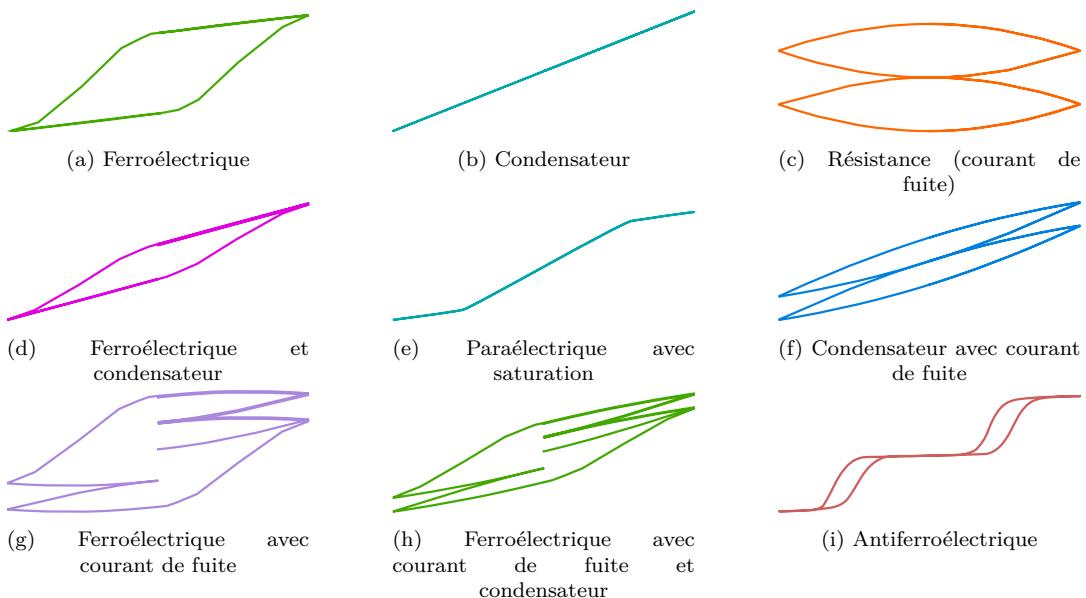

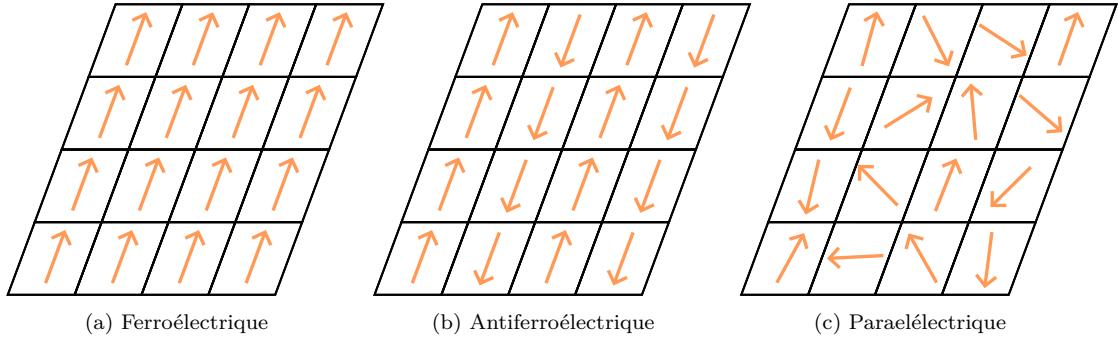

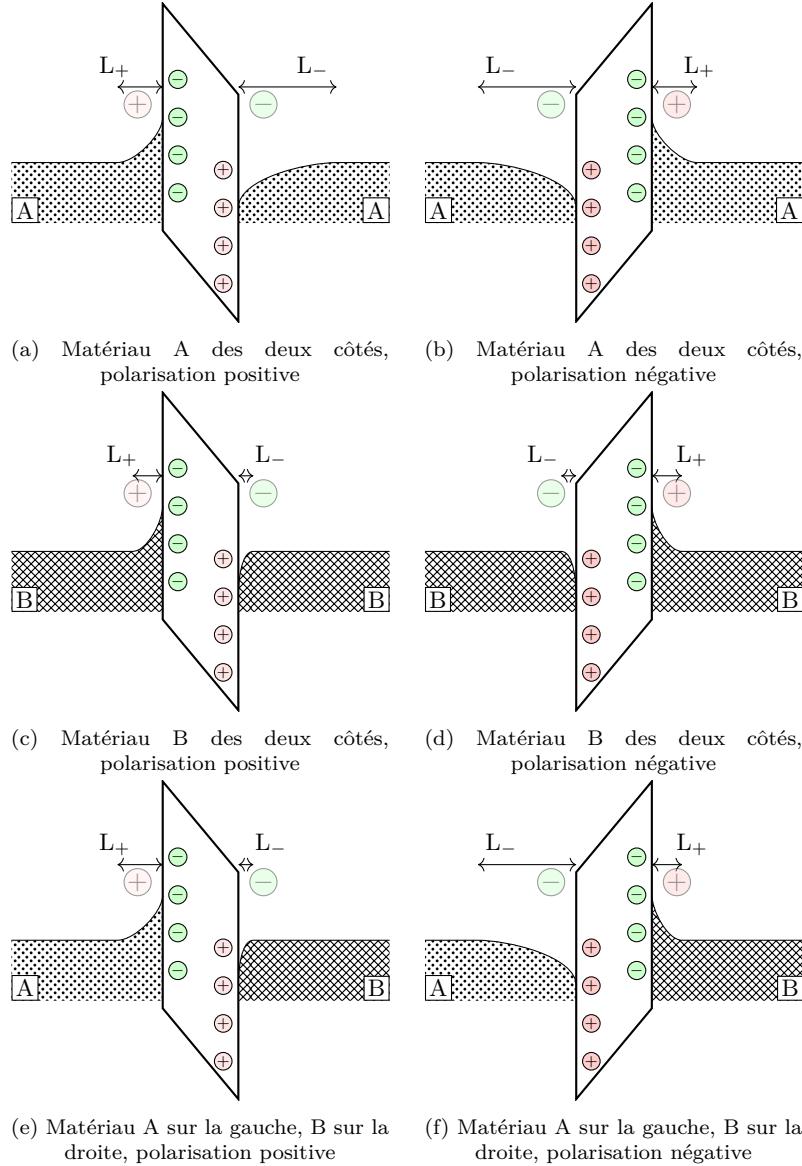

| 2.5  | Illustration de diverses courbes $P$ - $V$ . . . . .                                          | 33  |

| 2.6  | Polarisation électrique et lien avec la ferroélectricité. . . . .                             | 34  |

| 2.7  | Diagrammes de bandes avec zones de compensation de charges. . . . .                           | 35  |

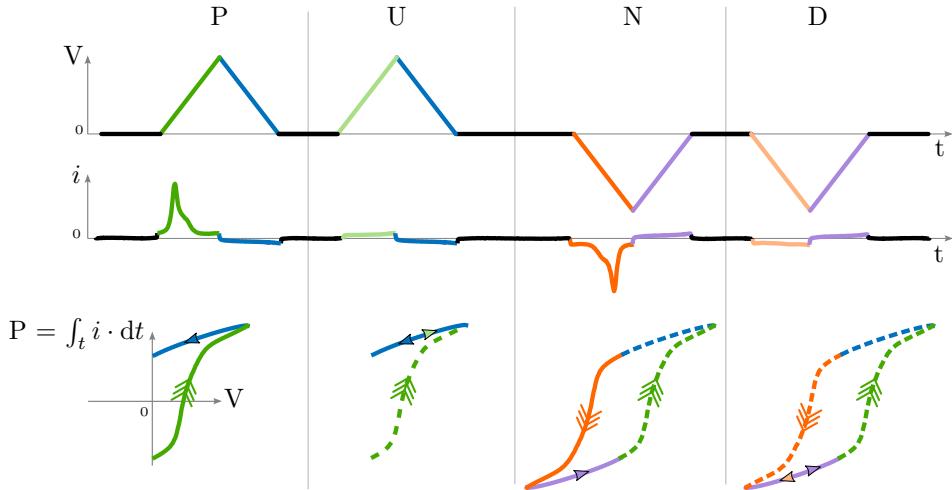

| 2.8  | Illustration d'une mesure PUND. . . . .                                                       | 36  |

| 2.9  | Réponse $P$ - $V$ purement ferroélectrique extraite par stimulation PUND . . . . .            | 38  |

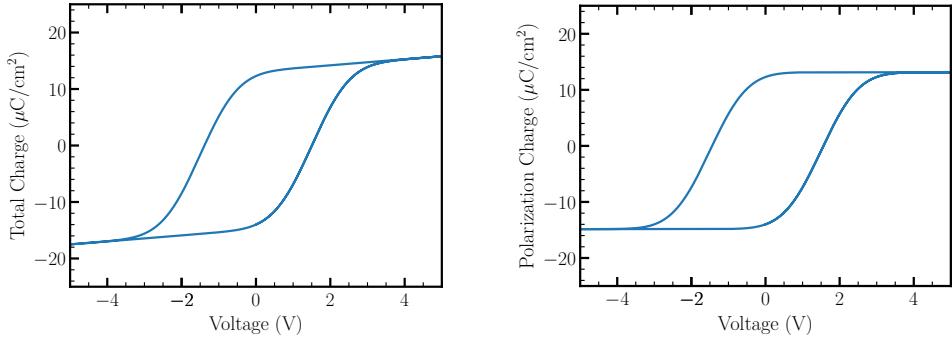

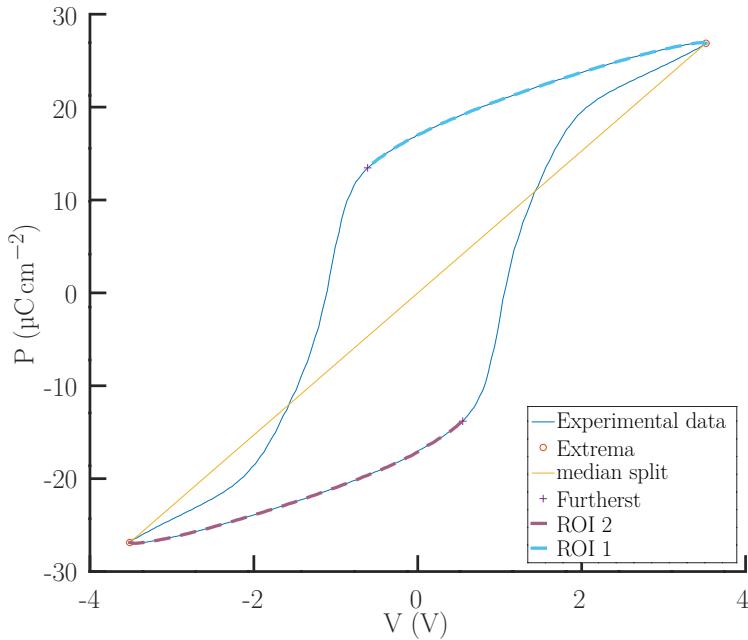

| 2.10 | Tracé de l'énergie libre de Gibbs et de sa dérivée pour le modèle Landau. . . . .             | 39  |

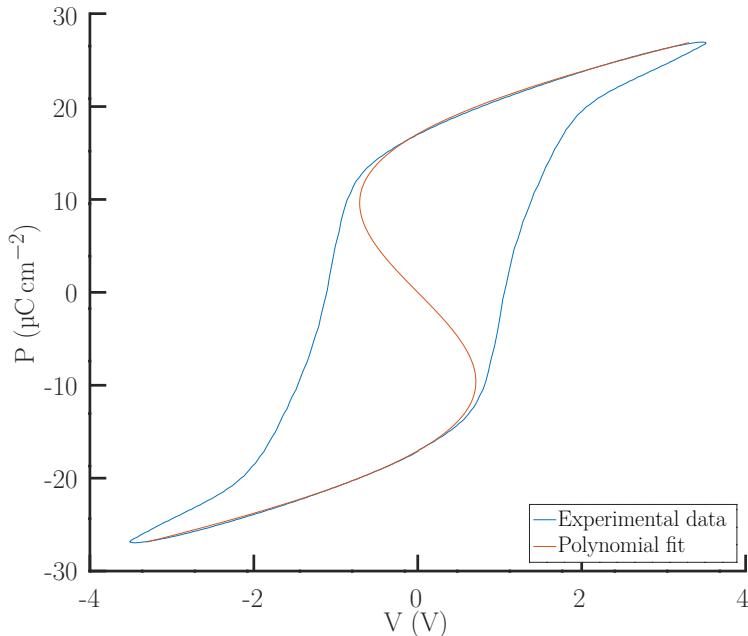

| 2.11 | Choix des coefficients Landau selon les données expérimentales. . . . .                       | 42  |

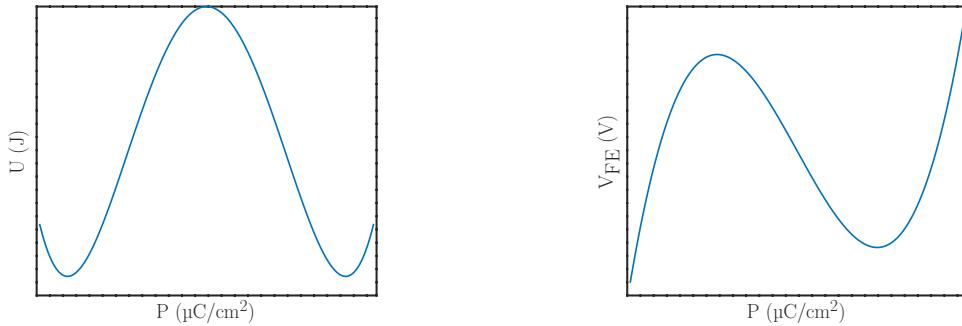

| 2.12 | Exemple de cycle d'hystérésis ferroélectrique. . . . .                                        | 43  |

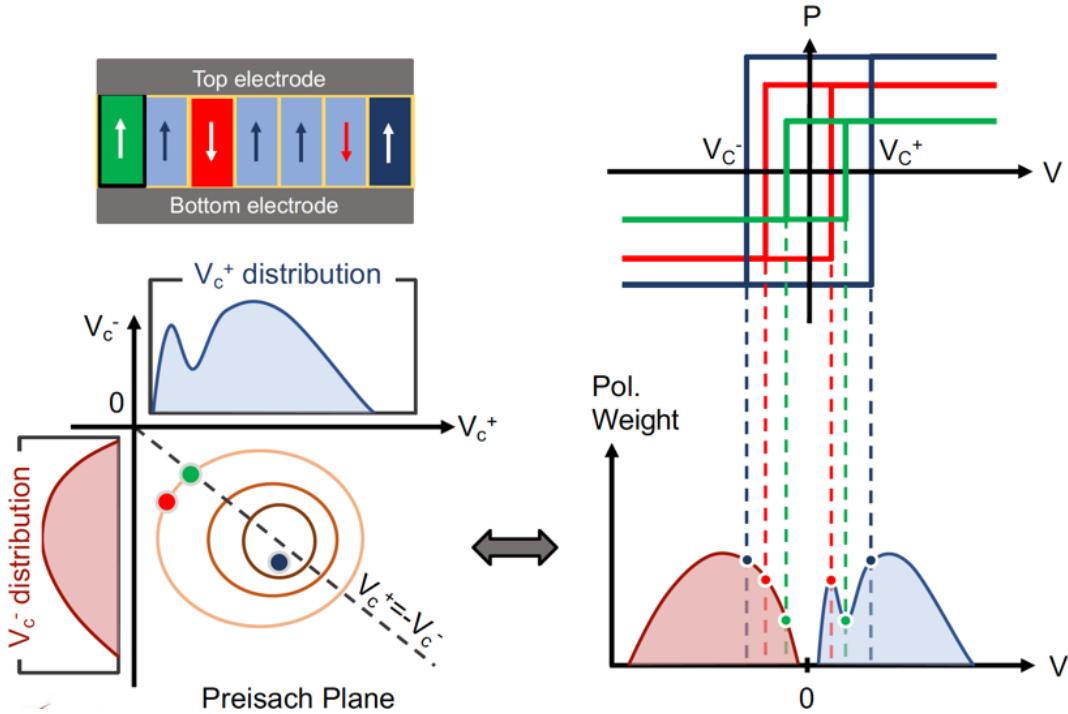

| 2.13 | Modèle de Preisach – hystérons et plan . . . . .                                              | 44  |

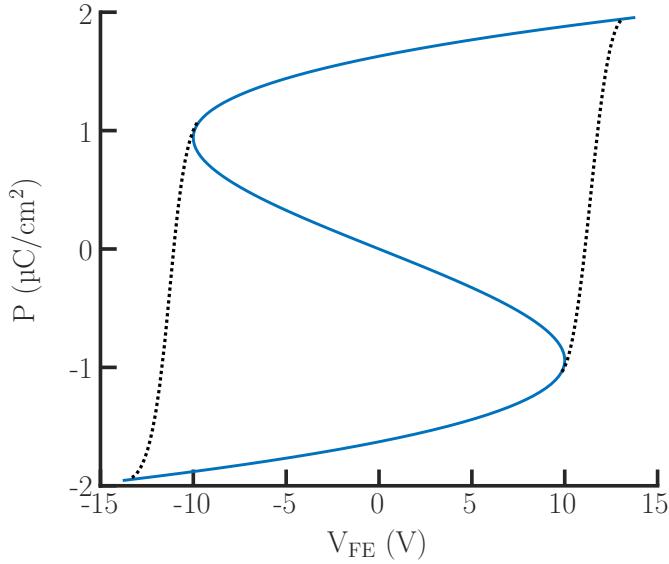

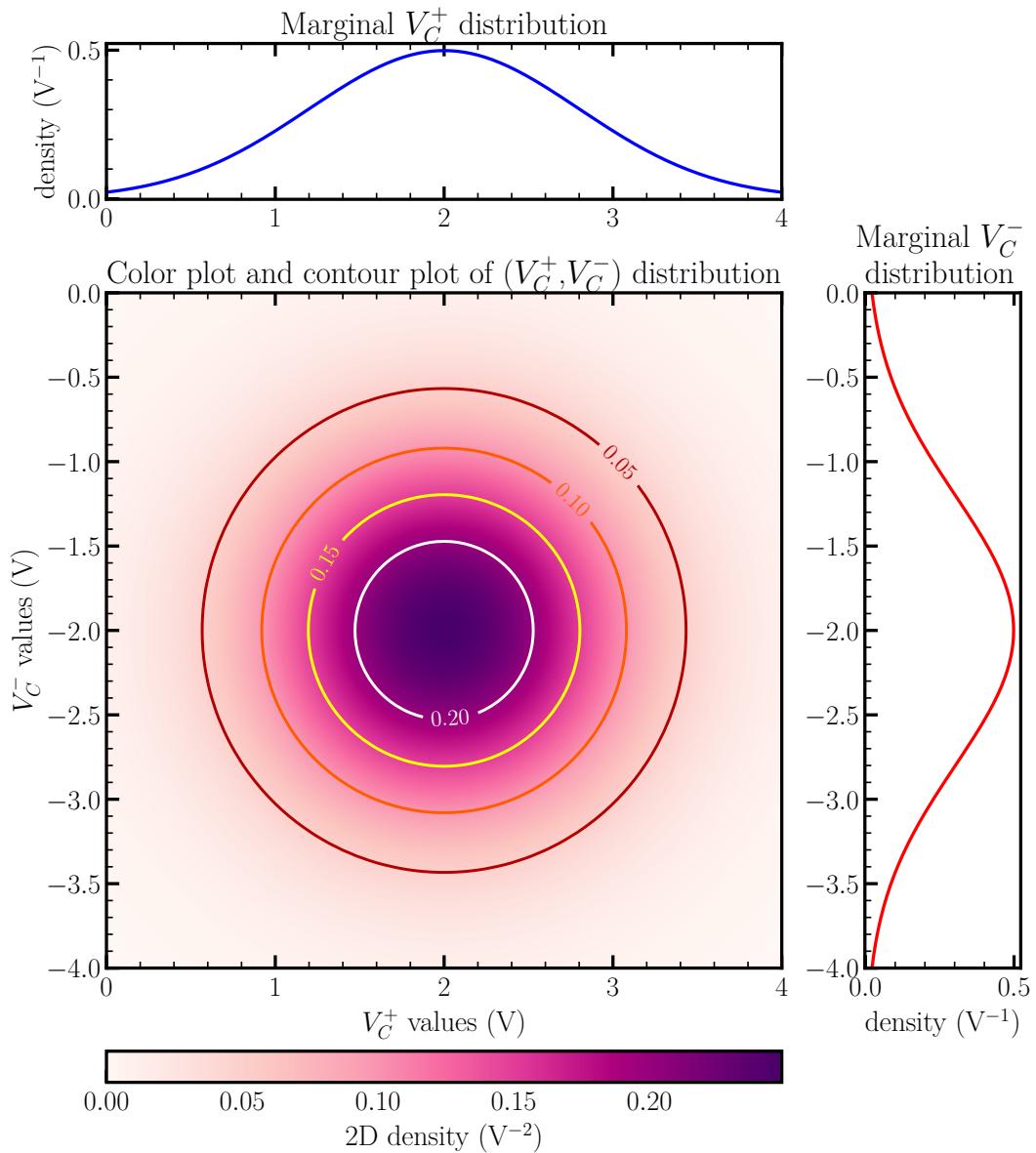

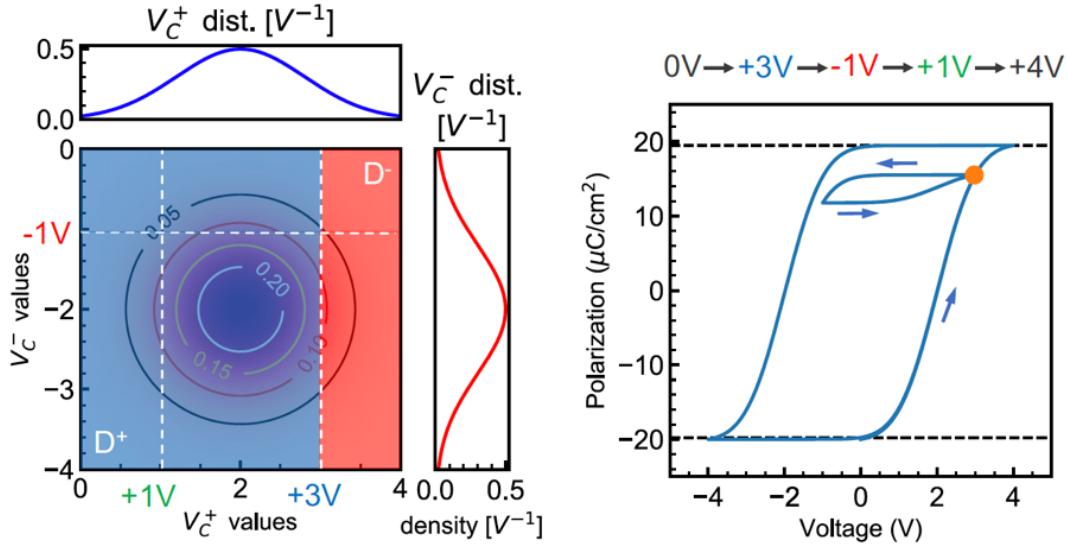

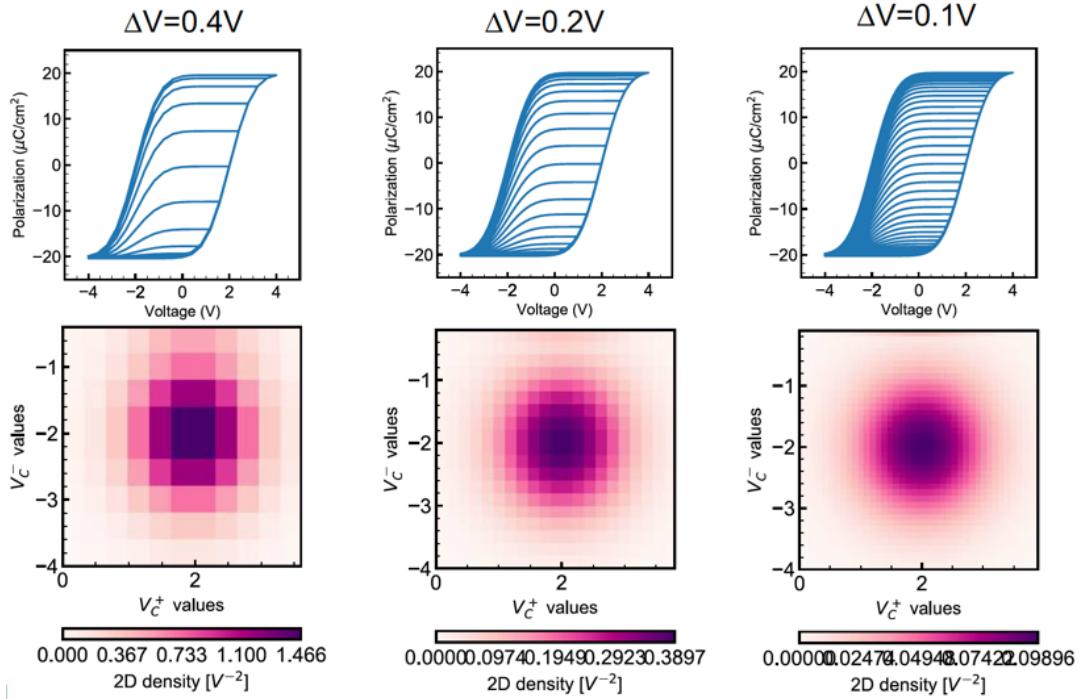

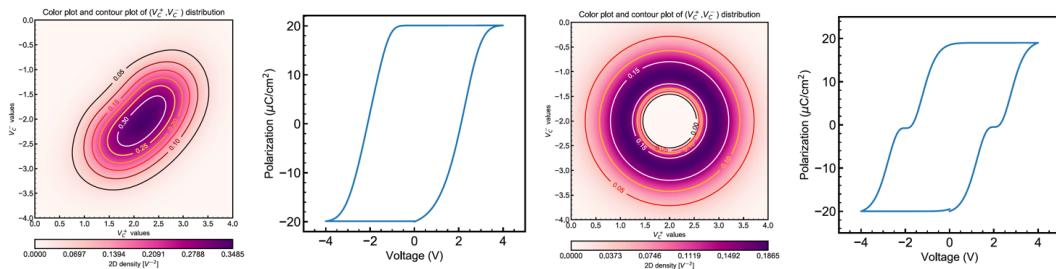

| 2.14 | Distribution Gaussienne 2D ( $V_c^+$ , $V_c^-$ ) . . . . .                                    | 45  |

| 2.15 | Boucles internes et points d'inflexion. . . . .                                               | 46  |

| 2.16 | Exemple d'extraction de distribution gaussienne 2D $V_c^+ / V_c^-$ . . . . .                  | 46  |

| 2.17 | Gestion de distributions $V_c^+ / V_c^-$ arbitraires. . . . .                                 | 46  |

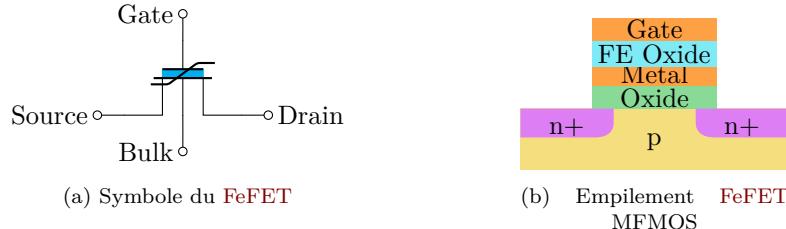

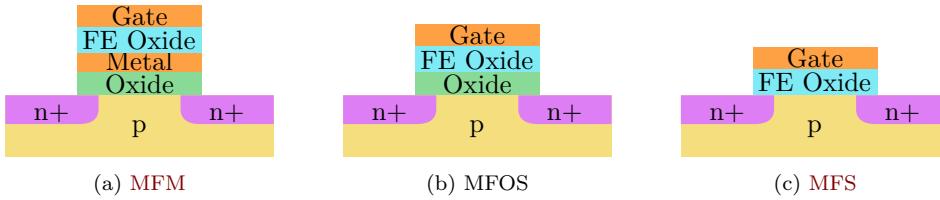

| 2.18 | Symbole du FeFET et empilement de grille. . . . .                                             | 50  |

| 2.19 | Empilements de grille de FeFETs. . . . .                                                      | 51  |

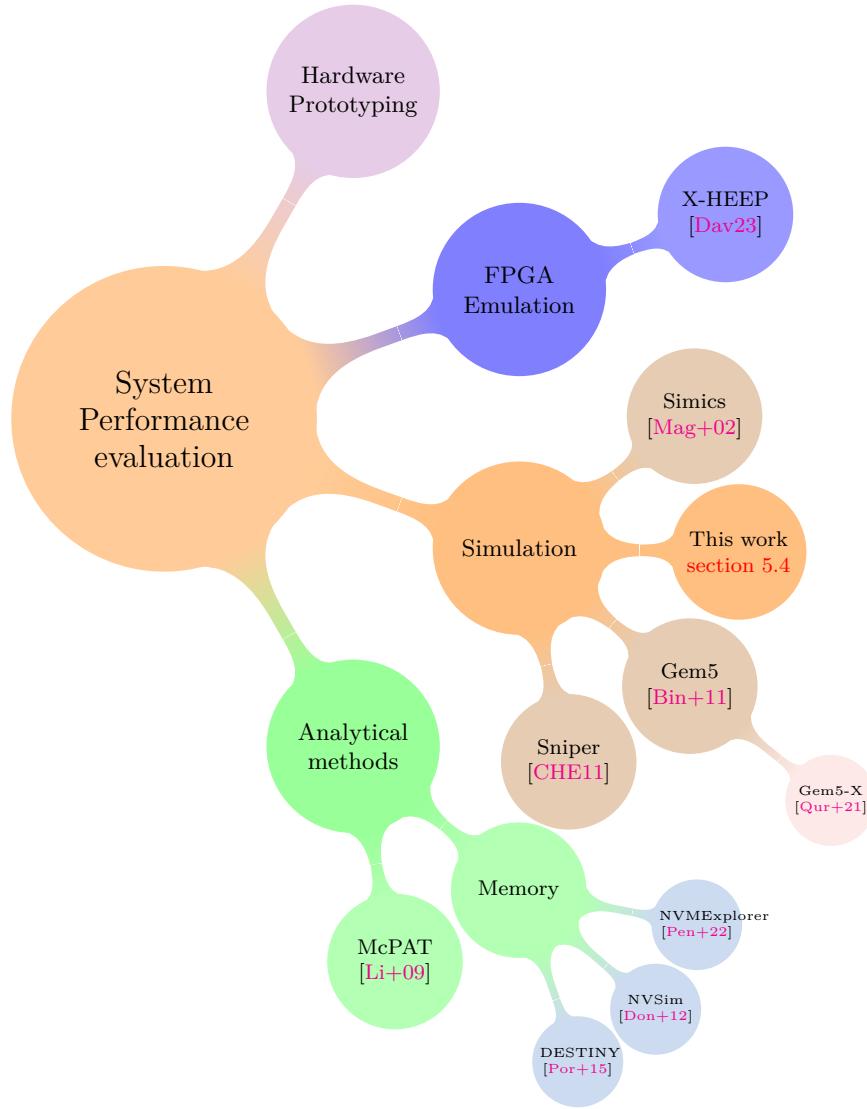

| 2.20 | Outils d'évaluation des performances au niveau du système. . . . .                            | 56  |

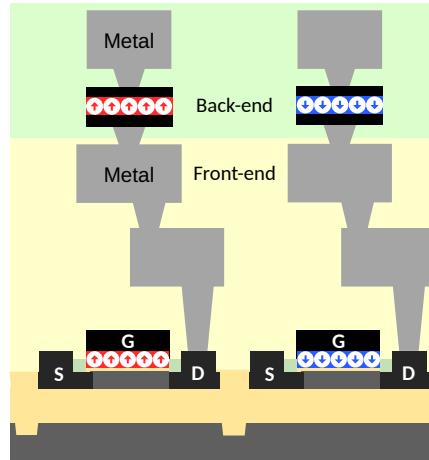

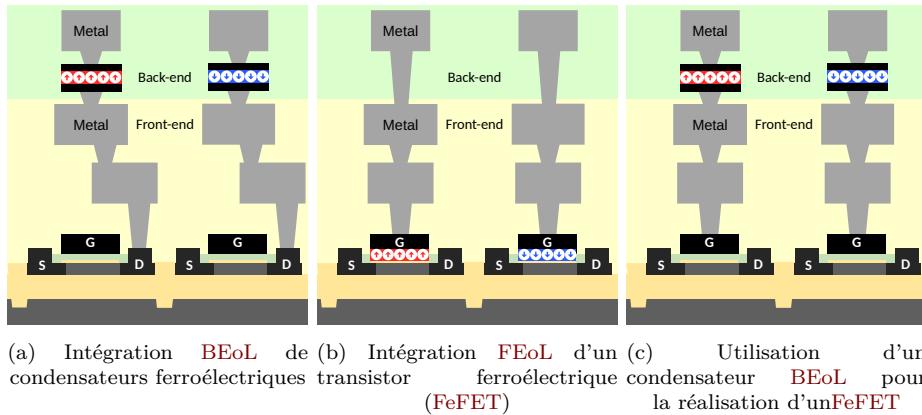

| 3.1  | Illustration des technologies ferroélectrique de tête et bout de ligne. . . . .               | 60  |

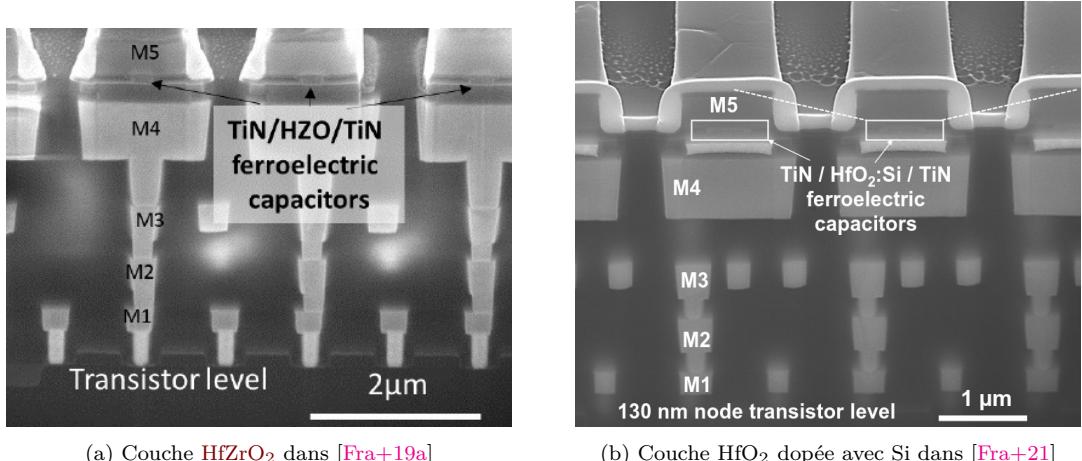

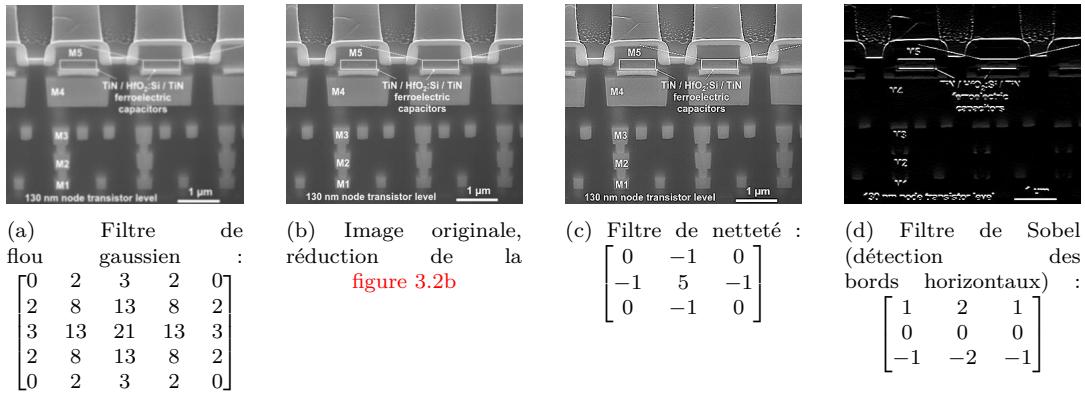

| 3.2  | Visualisation au microscope électronique des couches supérieures de MAD200. . . . .           | 61  |

| 3.3  | Comparaison de coupes d'empilement de FeFET et de PsFeFET. . . . .                            | 65  |

| 3.4  | Comparison cutaway of FEoL and BEoL ferroelectric technologies . . . . .                      | 66  |

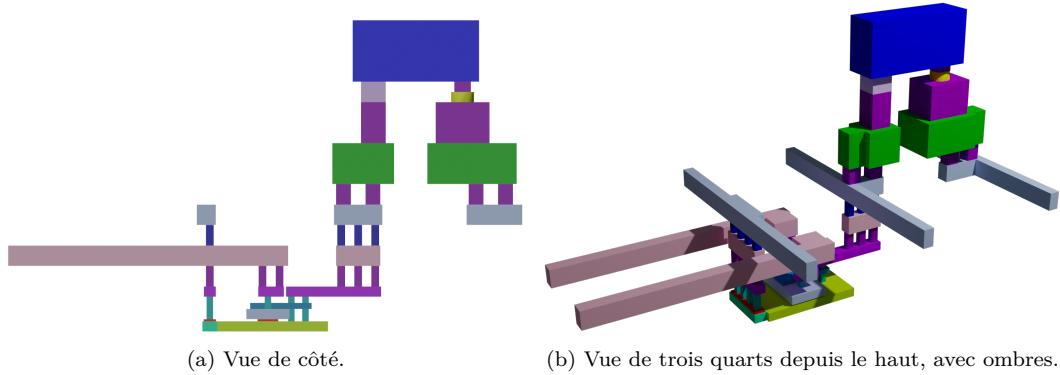

| 3.5  | Représentation 3D du PsFeFET. . . . .                                                         | 70  |

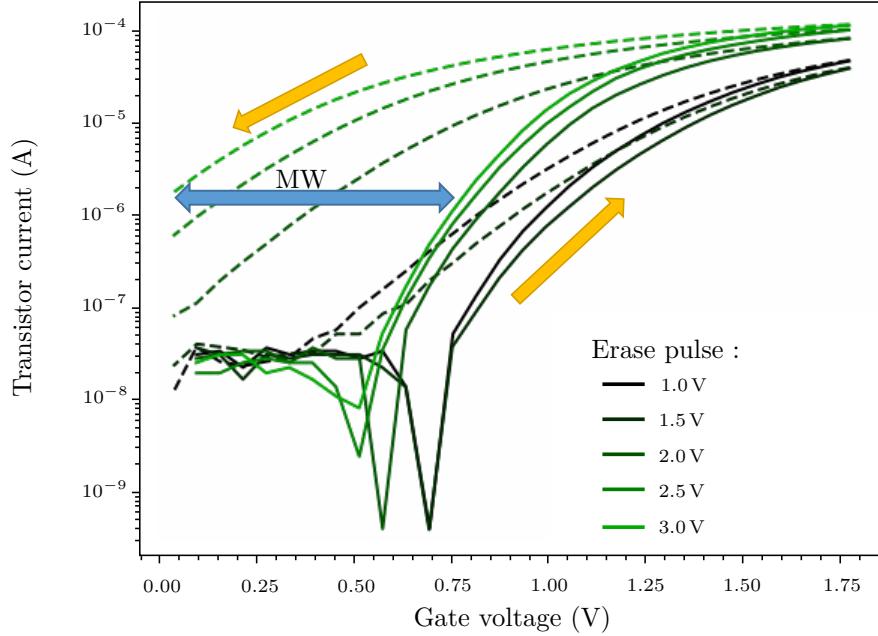

| 3.6  | Caractéristique $I_D = f(V_G)$ du PsFeFET. . . . .                                            | 71  |

| 3.7  | Tension de programmation et fenêtre de lecture du 2T1C. . . . .                               | 84  |

| 3.8  | Effet de la durée d'impulsion sur la fenêtre mémoire du 2T1C. . . . .                         | 84  |

| 4.1  | Illustration du décalage de $V_{th}$ . . . . .                                                | 89  |

| 4.2  | Comportement de la cellule Black & Das. . . . .                                               | 101 |

| 4.3  | Exemple de noyaux de filtre. . . . .                                                          | 103 |

| 4.4  | Illustration d'un filtre d'image convolutionnel. . . . .                                      | 104 |

| 4.5  | Schéma haut niveau du filtre d'image proposé . . . . .                                        | 105 |

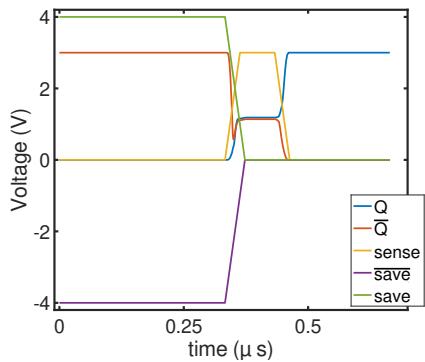

| 4.6  | Signaux d'entrée et de sortie du multiplexeur de tensions de programmation. . . . .           | 113 |

| 4.7  | Flot de vérification utilisé pour valider le circuit du filtre d'image . . . . .              | 115 |

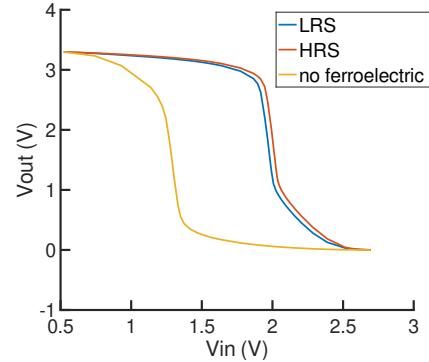

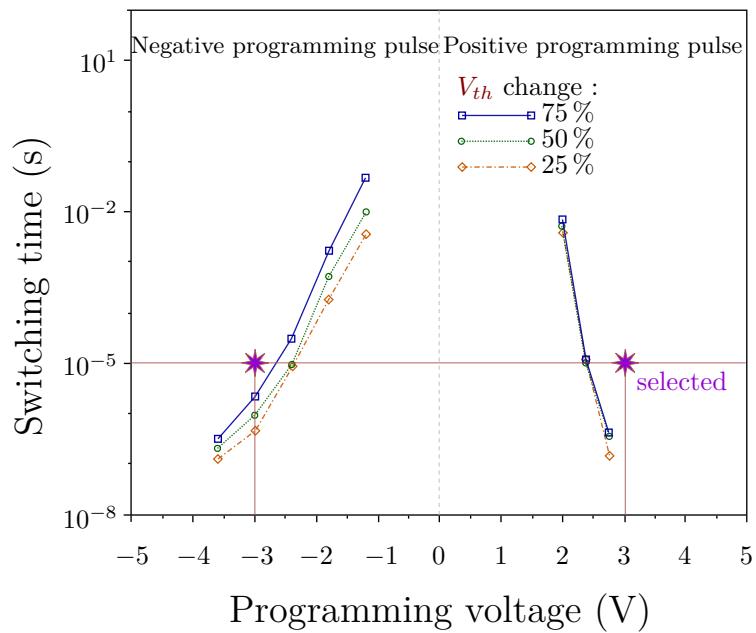

| 4.8  | Mesure du décalage de $V_{th}$ selon la durée et la tension des impulsions. . . . .           | 118 |

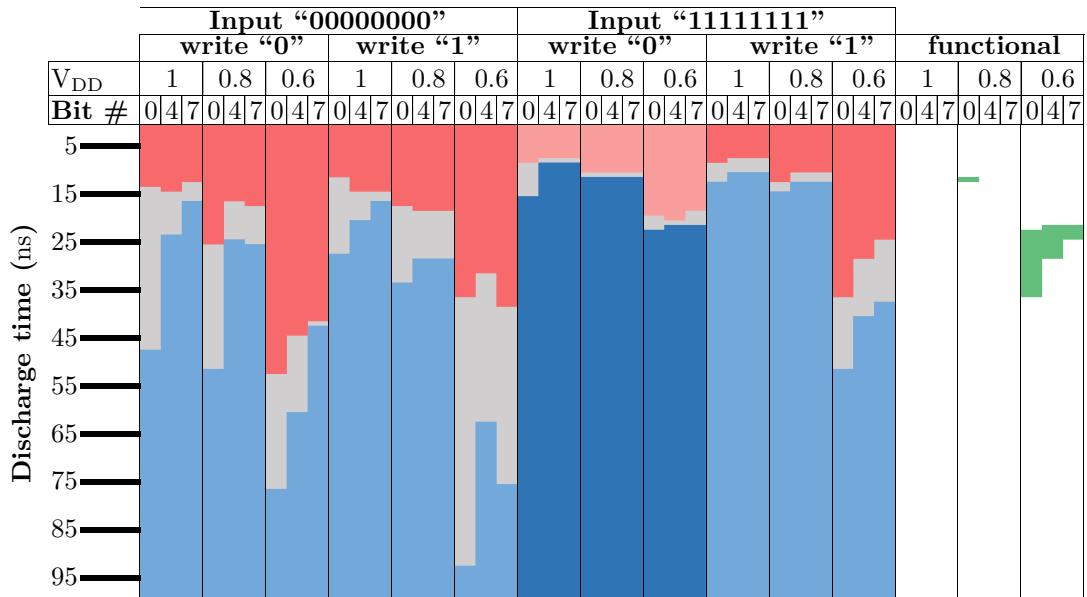

| 4.9  | Résultats de caractérisation dynamique du filtre d'image et point opérateur. . . . .          | 120 |

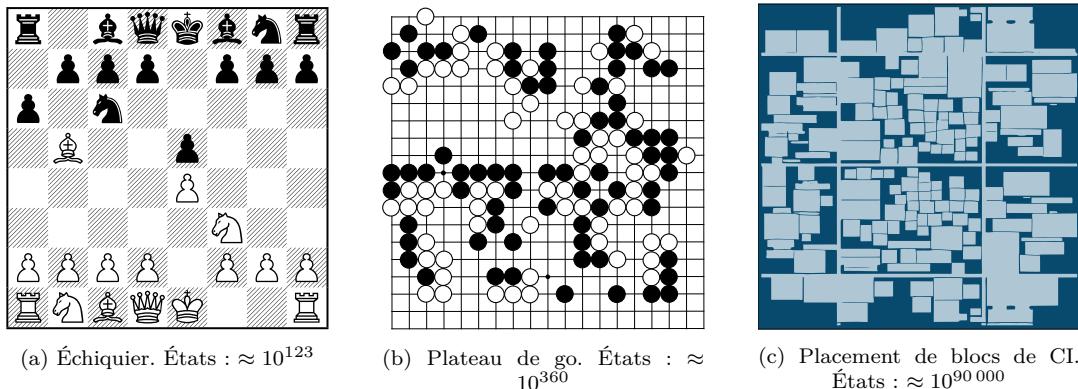

| 5.1  | Illustration de l'augmentation de la complexité due à l'explosion combinatoire. . . . .       | 124 |

| 5.2  | Espace des paramètres et de performances; ensemble et front de Pareto. . . . .                | 125 |

| 5.3  | Approches expérimentale et en simulation pour la mesure de performance. . . . .               | 126 |

| 5.4  | Approche d'exploration de l'espace de conception automatisée. . . . .                         | 127 |

| 5.5  | Flot de génération de l'ensemble et du front de Pareto . . . . .                              | 128 |

| 5.6  | Architecture de l'IPC Cadence. . . . .                                                        | 129 |

| 5.7  | Formes d'ondes de test pour cellule 1T1C, annotées. . . . .                                   | 131 |

|                                                                                             |     |

|---------------------------------------------------------------------------------------------|-----|

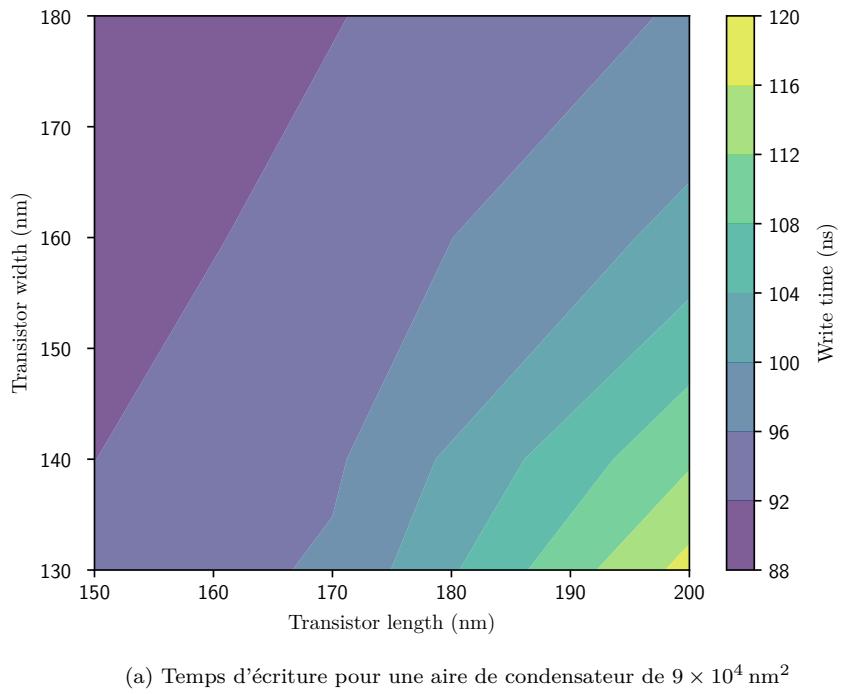

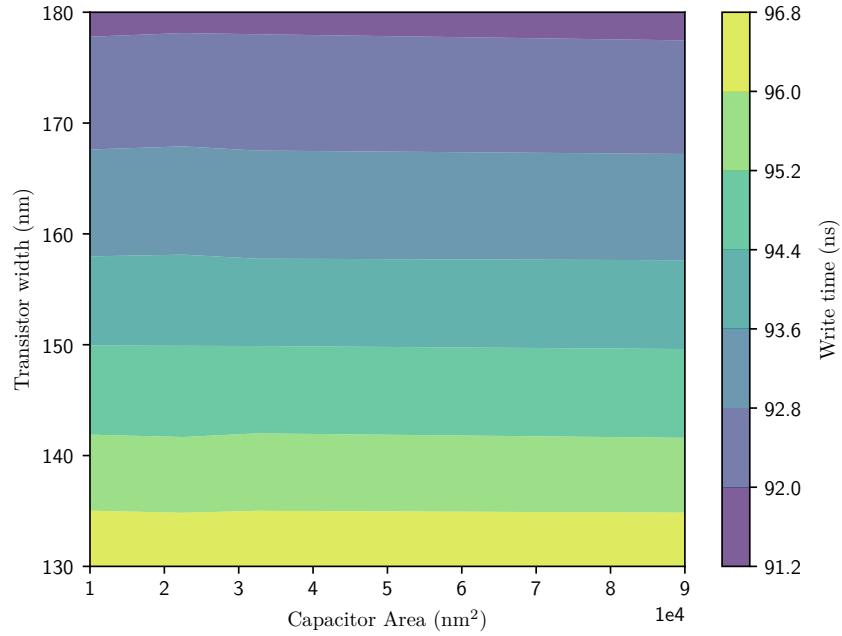

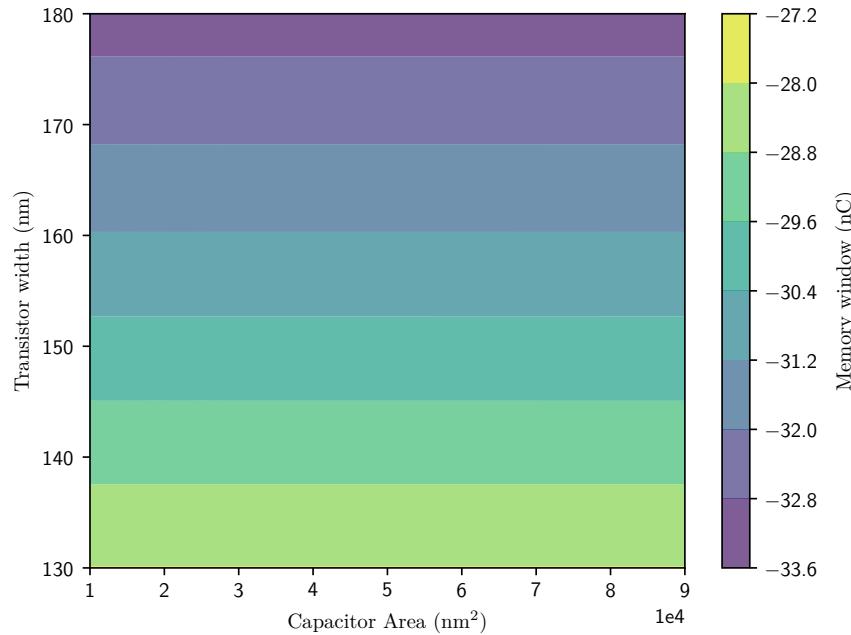

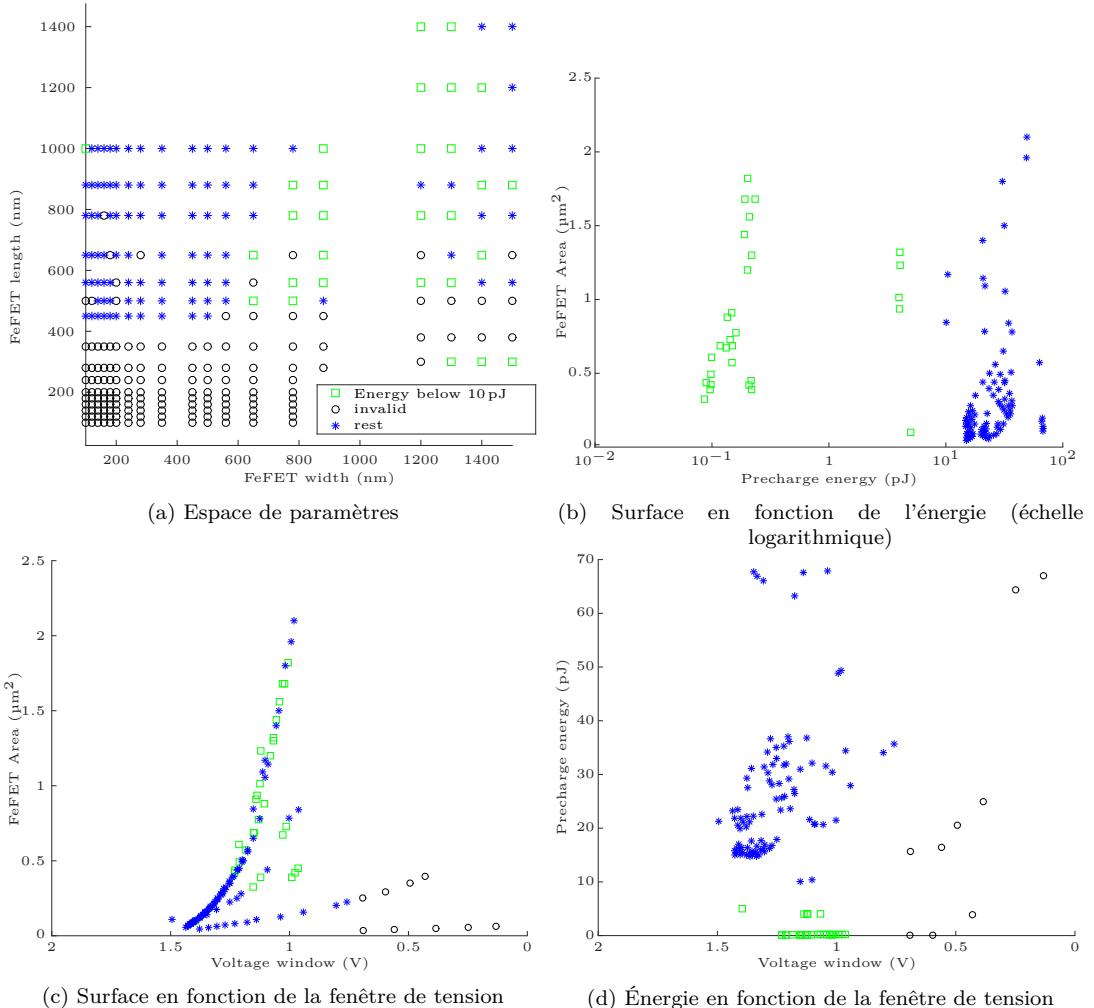

| 5.8 Résultats DSE 1T1C: temps, fenêtre mémoire vs géométrie du transistor. . . . .          | 135 |

| 5.9 Résultats DSE 1T1C: temps et énergie vs dimensions du condensateur. . . . .             | 136 |

| 5.10 DSE préliminaire de la porte NAND non volatile à FeFET. . . . .                        | 139 |

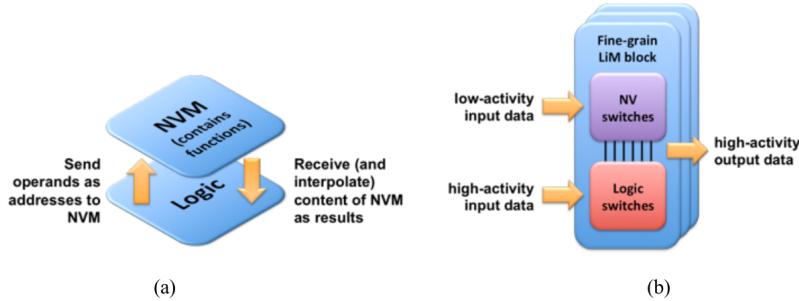

| 5.11 Concepts de LiM à grain fin et gros grain. . . . .                                     | 141 |

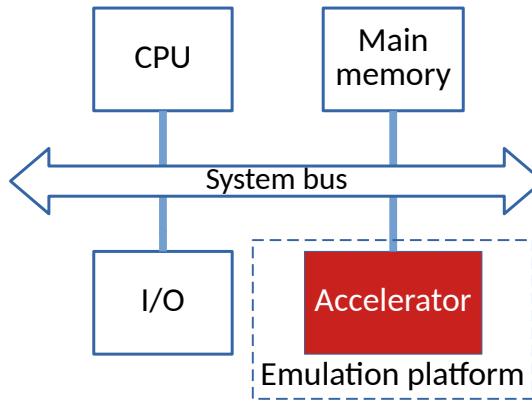

| 5.12 Localisation d'un accélérateur logique en mémoire sur le bus système. . . . .          | 141 |

| 5.13 Diagramme de l'architecture interne de la plate-forme d'évaluation. . . . .            | 142 |

| 5.14 Plate-forme de simulation: cartes modèles, gestionnaire d'opérations. . . . .          | 144 |

| 5.15 Illustration de l'interface d'opération commune. . . . .                               | 145 |

| 5.16 Diagramme d'exécution du module opérationnel. . . . .                                  | 145 |

| 5.17 Opération d'addition effectuée par l'accélérateur choisi pour exemple. . . . .         | 146 |

| 5.18 Entrées et sorties de la plate-forme d'évaluation des performances. . . . .            | 147 |

| 5.19 Résultats de la plate-forme d'évaluation pour calcul normalement-éteint. . . . .       | 149 |

| 5.20 Exploration des compromis LiM: interpolateur vs multiplicateur à LUT. . . . .          | 150 |

| 5.21 Consommation d'énergie des stratégies de multiplication matricielle WB et NWB. . . . . | 151 |

| 5.22 Flot DTCO combinant la performance du système et paramètres des dispositifs. . . . .   | 153 |

# Liste des Circuits

|      |                                                                                      |     |

|------|--------------------------------------------------------------------------------------|-----|

| 3.1  | Cellule mémoire 1T1C. . . . .                                                        | 61  |

| 3.2  | Tableau 1T1C $4 \times 4$ . . . . .                                                  | 62  |

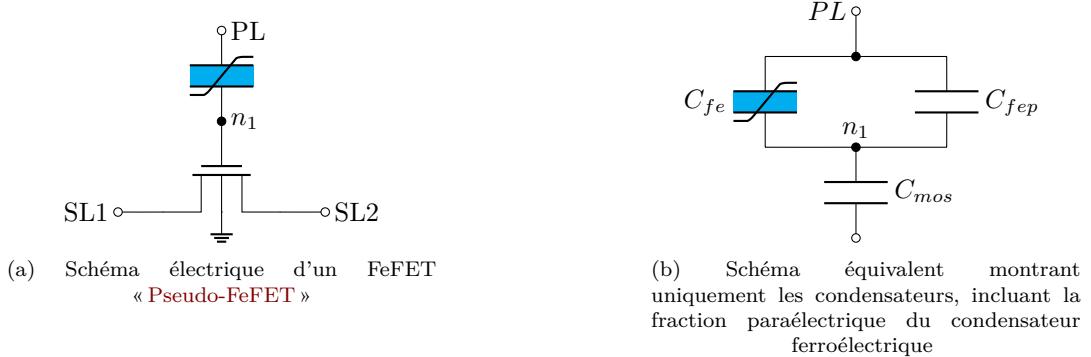

| 3.3  | Circuits électriques du PsFeFET et du FeFET. . . . .                                 | 65  |

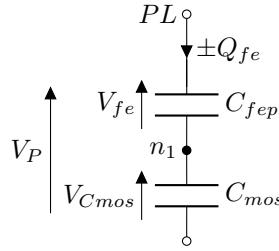

| 3.4  | PsFeFET et schéma équivalent. . . . .                                                | 67  |

| 3.5  | Condensateurs flottants équivalents du circuit PsFeFET. . . . .                      | 68  |

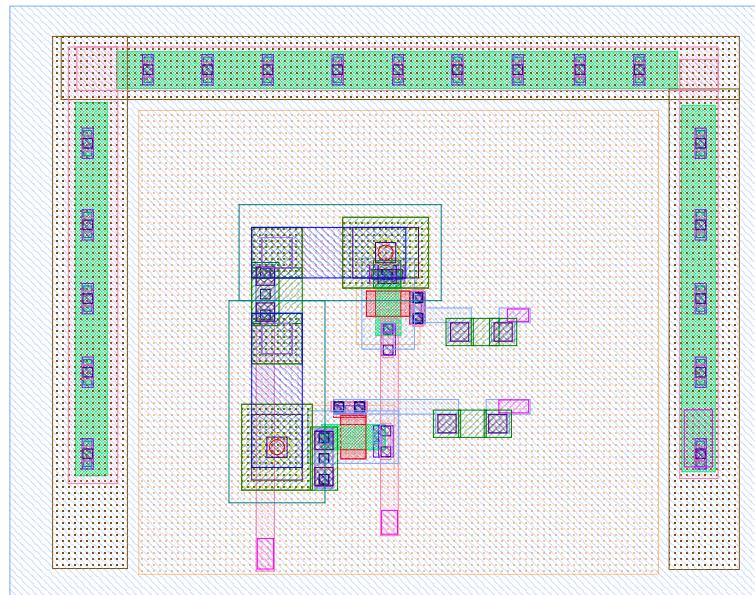

| 3.6  | Layout du PsFeFET. . . . .                                                           | 69  |

| 3.7  | CMOS à PsFeFET partageant une unique FeCap. . . . .                                  | 72  |

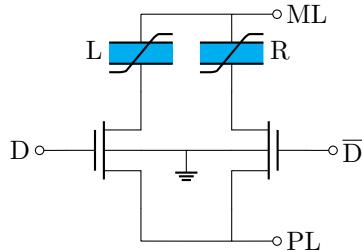

| 3.8  | Schéma de TCAM à lecture destructive. . . . .                                        | 73  |

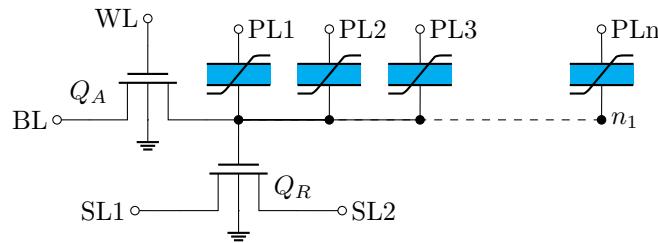

| 3.9  | Layout de la TCAM à lecture destructive. . . . .                                     | 76  |

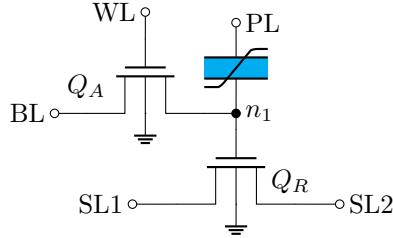

| 3.10 | Schéma de la cellule 2T1C telle que conçue. . . . .                                  | 77  |

| 3.11 | Schéma de la cellule 2TnC. . . . .                                                   | 79  |

| 3.12 | Layout de la cellule 2T1C. . . . .                                                   | 81  |

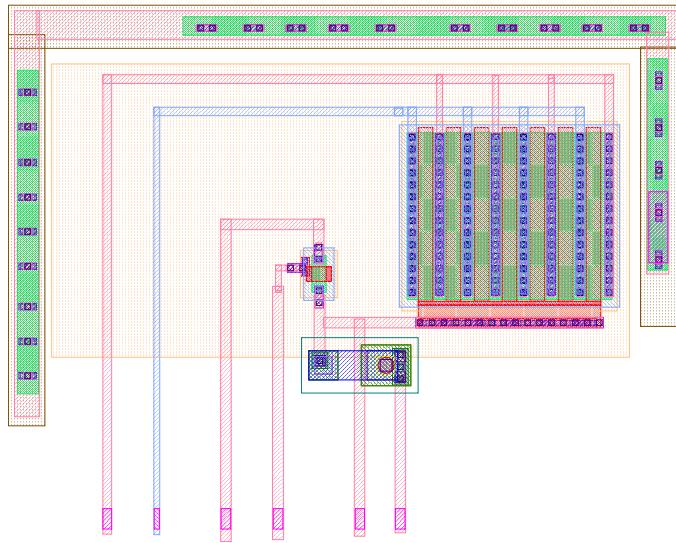

| 3.13 | Structure 2T3C telle que conçue. . . . .                                             | 82  |

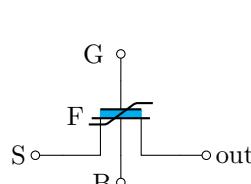

| 4.1  | Symbol du FeFET . . . . .                                                            | 87  |

| 4.2  | Cellule 1T-FeFET. . . . .                                                            | 92  |

| 4.3  | Tableau 1T-FeFET $4 \times 4$ . . . . .                                              | 92  |

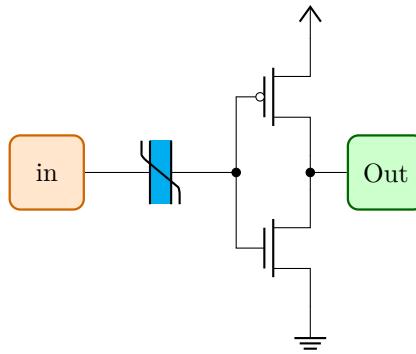

| 4.4  | Circuit de transrésistance avec FeFET complémentaire. . . . .                        | 95  |

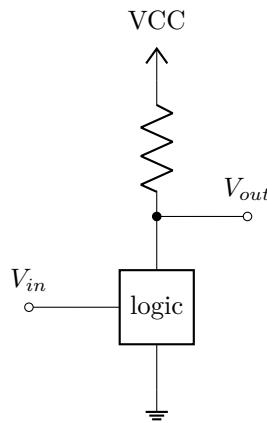

| 4.5  | Circuit résistance-FeFET. . . . .                                                    | 96  |

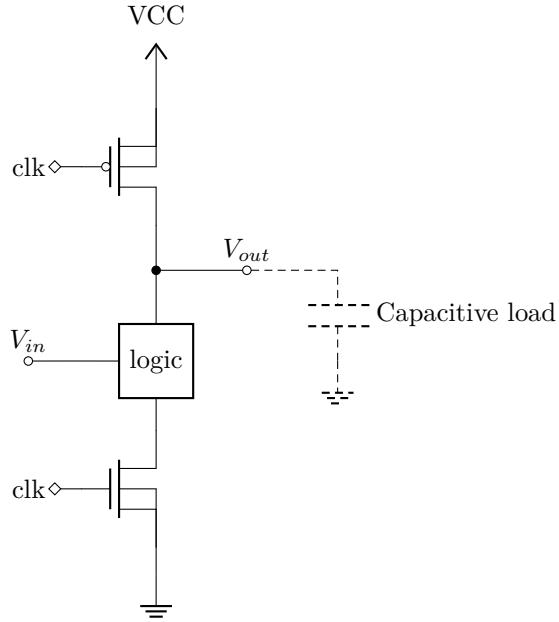

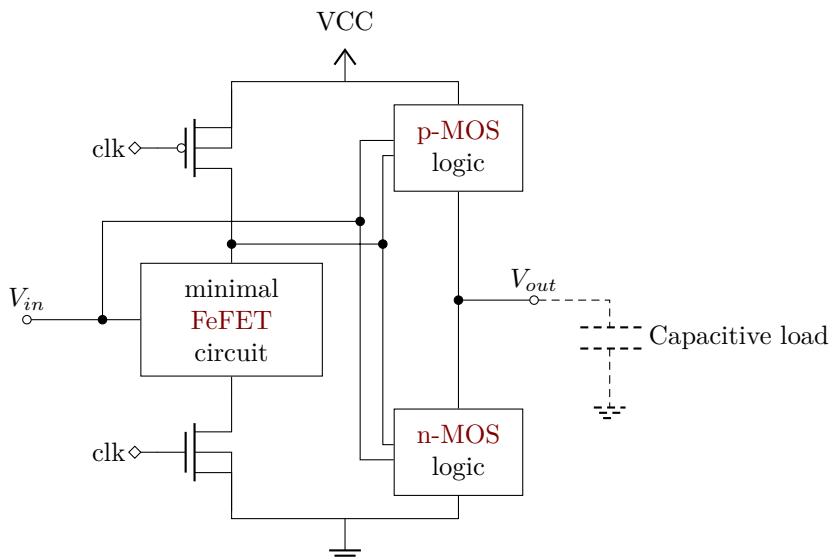

| 4.6  | Transrésistance par logique dynamique. . . . .                                       | 97  |

| 4.7  | Architecture hybride CMOS et logique dynamique . . . . .                             | 97  |

| 4.8  | Porte de transmission à FeFET et table de vérité. . . . .                            | 98  |

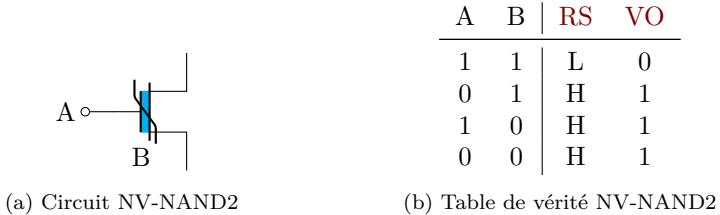

| 4.9  | Porte logique NAND à FeFETs. . . . .                                                 | 99  |

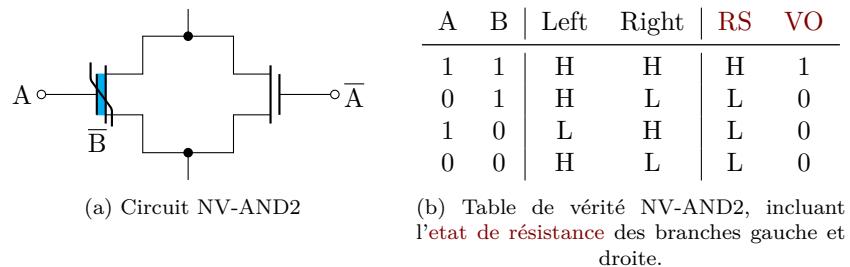

| 4.10 | Porte logique ET à FeFET. . . . .                                                    | 99  |

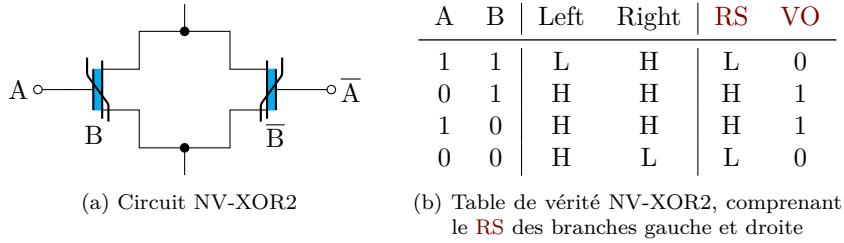

| 4.11 | XOR FeFET-based logic gate . . . . .                                                 | 100 |

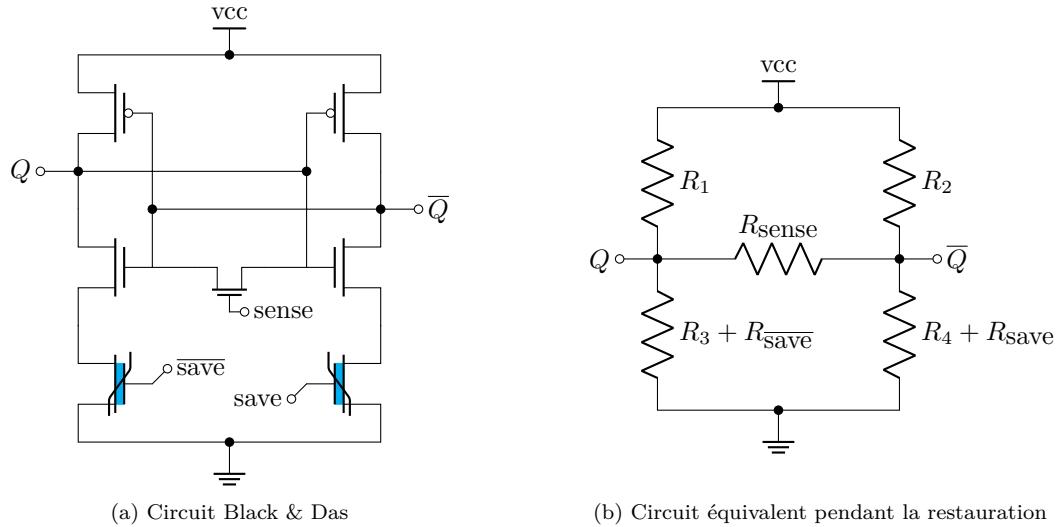

| 4.12 | SRAM Black & Das à FeFET. . . . .                                                    | 101 |

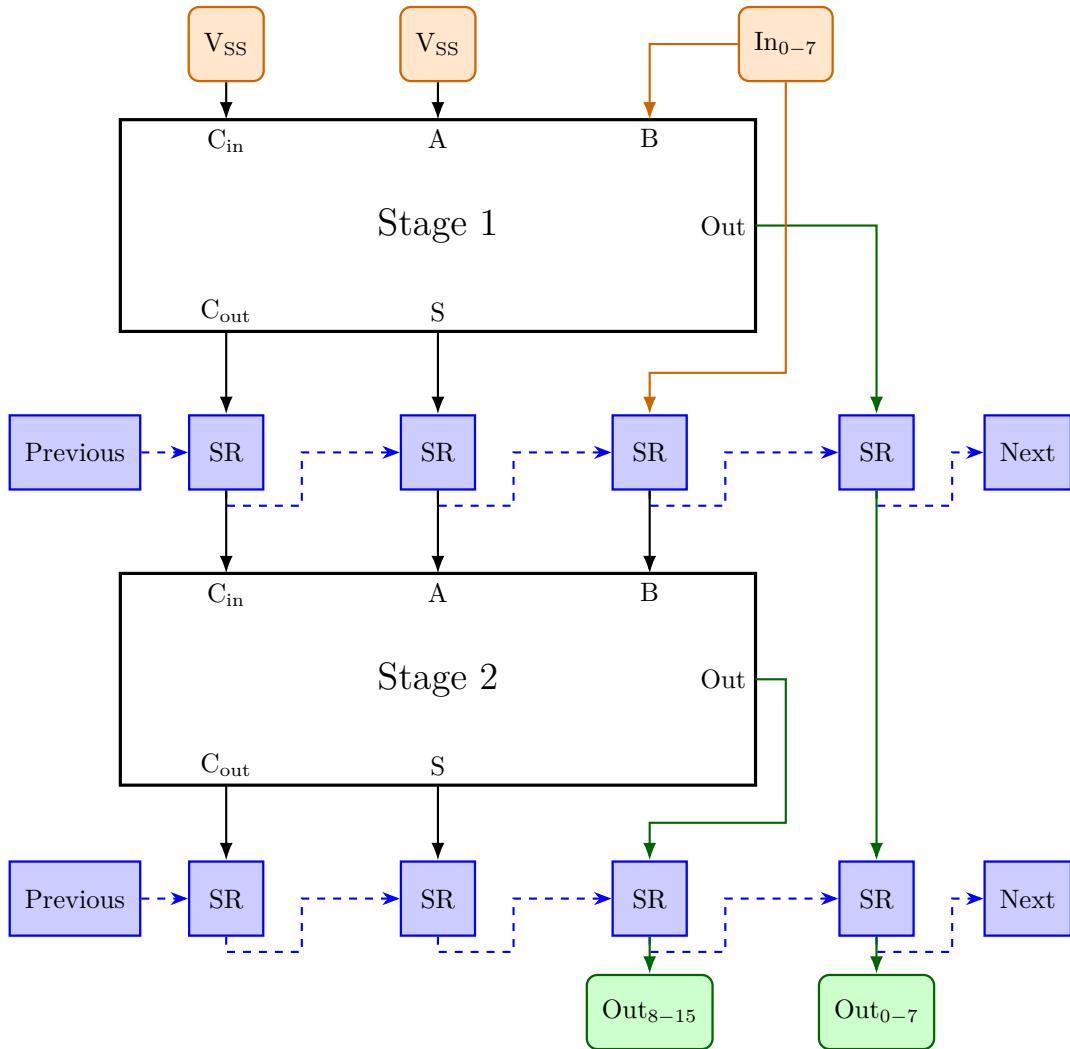

| 4.13 | Architecture du filtre d'image. . . . .                                              | 106 |

| 4.14 | Schéma interne du registre à décalage. . . . .                                       | 107 |

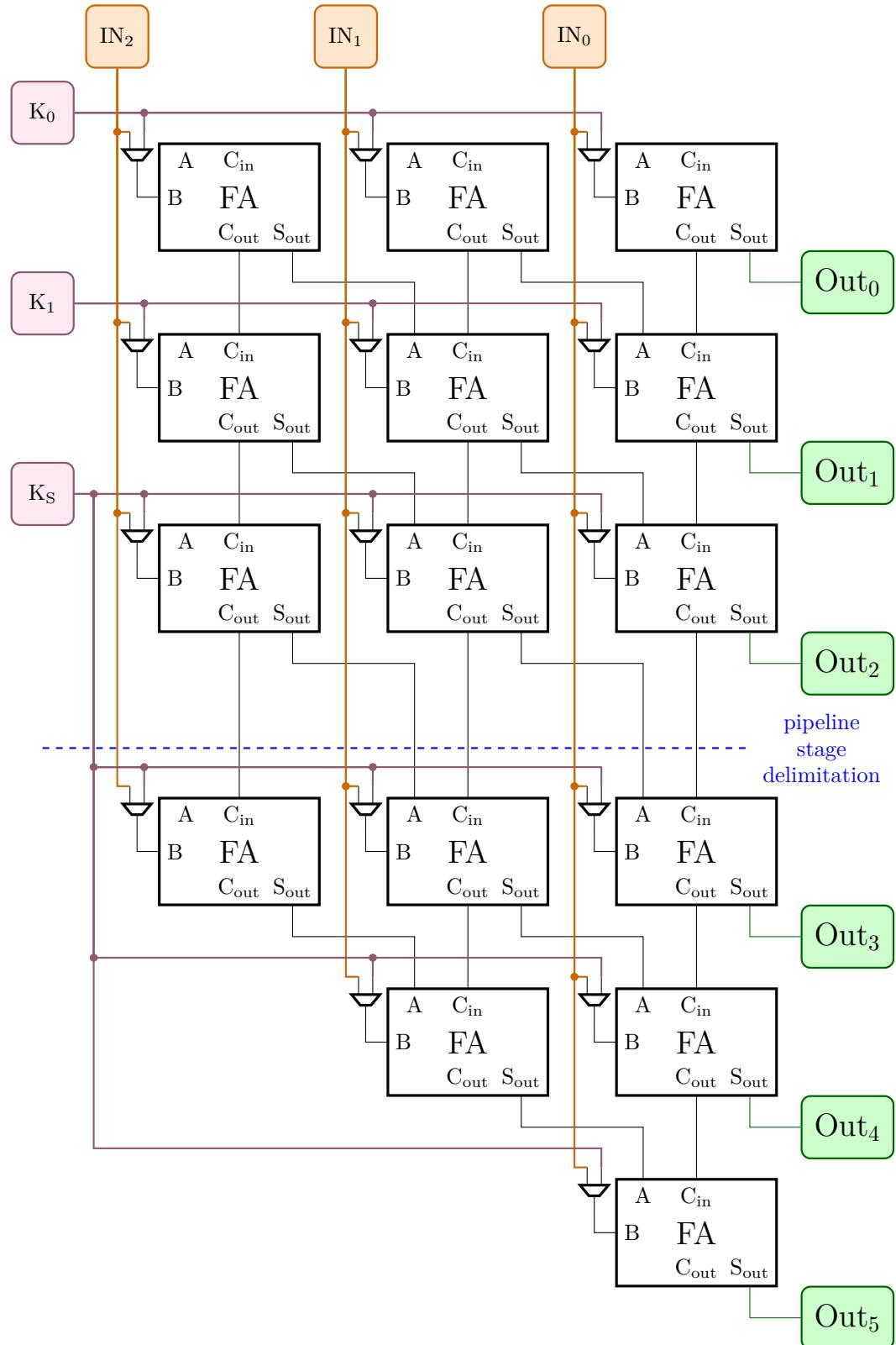

| 4.15 | Circuit final de l'additionneur complet à FeFET. . . . .                             | 109 |

| 4.16 | Additionneur à propagation de retenue à additionneurs complets. . . . .              | 110 |

| 4.17 | Étages de pipeline du multiplicateur du filtre d'images. . . . .                     | 111 |

| 4.18 | Multiplexeur de tension utilisé pour programmer le FeFET du multiplicateur. . . . .  | 113 |

| 5.1  | Cellule 1T1C et générateurs de tension pour caractérisation. . . . .                 | 130 |

| 5.2  | Circuit non-volatile NV-NAND2 dynamique utilisé pour la DSE. . . . .                 | 137 |

| B.1  | Première version de l'additionneur complet pour le circuit multiplicateur. . . . .   | 195 |

| B.2  | Deuxième itération de l'additionneur complet pour le circuit multiplicateur. . . . . | 196 |

| B.3  | Circuit Cadence pour le banc d'essai 1T1C. . . . .                                   | 196 |

# Liste des extraits de code

|      |                                                                                    |     |

|------|------------------------------------------------------------------------------------|-----|

| 2.1  | Modèle Verilog-A minimal de ferroélectrique . . . . .                              | 47  |

| 5.1  | Structure de carte modèle mémoire . . . . .                                        | 145 |

| 5.2  | Structure de carte modèle de module d'opération . . . . .                          | 146 |

| 5.3  | Trace d'exécution d'une addition . . . . .                                         | 146 |

| A.1  | Code SKILL® pour extraction de métriques depuis simulations de bitcell 1T1C        | 179 |

| A.2  | Code SKILL pour extraction de métriques de simulation de NAND à FeFET              | 181 |

| A.7  | Code GNU Octave de calcul de coefficients de Landau expérimentaux . . . . .        | 182 |

| A.3  | Script Python d'exploration d'espace de conception 1T1C . . . . .                  | 183 |

| A.4  | Script d'exploration de la NAND non volatile à FeFET . . . . .                     | 184 |

| A.5  | Sérialiseur de données en Verilog-A . . . . .                                      | 185 |

| A.6  | Sérialiseur de données en Verilog-A avec signal d'activation . . . . .             | 186 |

| A.8  | Code GNU Octave pour la projection orthogonale (dépendance) . . . . .              | 189 |

| A.9  | Code GNU Octave code pour régression polynomiale contrainte (dépendance)           | 189 |

| A.10 | Code GNU Octave pour le filtrage d'images par noyaux convolutifs . . . . .         | 190 |

| A.11 | Description Verilog du registre à décalage sur front descendant et debug . . . . . | 190 |

| A.12 | Description Verilog du registre à décalage et debug sur double front . . . . .     | 191 |

| A.13 | Description Verilog synthétisée d'un registre à décalage 1 bit . . . . .           | 192 |

| A.14 | Banc d'essai Verilog de programmation du noyau du filtre d'image à FeFET .         | 193 |

# Chapitre 1

# Introduction

## Contents

|                                                                              |           |

|------------------------------------------------------------------------------|-----------|

| <b>2.1 Ferroélectricité</b> . . . . .                                        | <b>27</b> |

| 2.1.1 Cristaux ferroélectriques . . . . .                                    | 27        |

| 2.1.2 Courbe $P-V$ . . . . .                                                 | 31        |

| 2.1.3 Relation avec la capacité et la paraélectricité . . . . .              | 32        |

| 2.1.4 Mesures PUND . . . . .                                                 | 36        |

| <b>2.2 Modélisation</b> . . . . .                                            | <b>38</b> |

| 2.2.1 Modèle de Landau . . . . .                                             | 38        |

| 2.2.2 Modèle de Preisach . . . . .                                           | 41        |

| 2.2.3 Modèle simplifié pour les simulations à grande échelle . . . . .       | 47        |

| <b>2.3 Condensateurs ferroélectriques</b> . . . . .                          | <b>48</b> |

| 2.3.1 Condensateur ordinaire . . . . .                                       | 48        |

| 2.3.2 Non-volatilité . . . . .                                               | 48        |

| 2.3.3 Capacité négative . . . . .                                            | 49        |

| <b>2.4 Transistors ferroélectriques</b> . . . . .                            | <b>50</b> |

| 2.4.1 Dispositifs FeFET . . . . .                                            | 50        |

| 2.4.2 Empilements de grille . . . . .                                        | 51        |

| 2.4.3 Modélisation . . . . .                                                 | 52        |

| <b>2.5 État de l'art des circuits ferroélectriques</b> . . . . .             | <b>52</b> |

| 2.5.1 Hafnium ferroélectrique . . . . .                                      | 52        |

| 2.5.2 Conception de circuits Condensateur Ferroélectriques et bout de ligne  | 53        |

| 2.5.3 Circuits utilisant des transistors à effet de champ ferroélectriques . | 53        |

| 2.5.4 Comparaison avec d'autres Mémoires non volatiles . . . . .             | 54        |

| 2.5.5 Exploration de l'espace de conception . . . . .                        | 54        |

| 2.5.6 Évaluation des performances au niveau du système . . . . .             | 56        |

## 1.1 À propos de ce document

### 1.1.1 Licence

This work is licensed under a [Creative Commons « Attribution 4.0 International » license](https://creativecommons.org/licenses/by/4.0/).

Pour résumer, cela signifie que vous êtes libre d'utiliser à la fois le texte (y compris le code) et les images de ce document, ainsi que de l'adapter et de le réutiliser au sein d'un autre document, à condition de respecter l'attribution (citation de la source et nom de l'auteur, ainsi que la nature des changements apportés). Pour plus de détails, veuillez consulter le lien ci-dessus ou le site web de Creative Commons à l'adresse suivante : <https://creativecommons.org/licenses/by/4.0/deed.en>. Cette licence ne s'applique pas aux figures fournies par des sources externes, comme indiqué dans les légendes.

### 1.1.2 Liens internes et code couleur

Ce document contient des liens internes et externes qui peuvent être suivis par un lecteur compatible. Ces liens sont codés par couleur comme suit :

1. **Liens internes** vers les sections, les figures, les extraits de code et les différentes parties du document

2. **Liens internes** vers la section **Bibliographie**

3. **Liens internes** vers le **Glossaire** et la liste des **Acronymes**

4. **Liens externes** vers des sites web

### 1.1.3 Code source du document, errata et matériel supplémentaire

Une révision à jour de ce document, ainsi que son code source **L<sup>A</sup>T<sub>E</sub>X** et des documents supplémentaires (extraits de codes et données additionnelles) sont disponibles à l'adresse <https://these.mayeul.net><sup>1</sup>.

### 1.1.4 Objectif du présent document

Ce document a pour but de résumer le travail accompli et les résultats obtenus au cours de ce doctorat, ainsi que de servir de document d'introduction à la conception de circuits ferroélectriques.

## 1.2 Contexte

Pendant des décennies, l'industrie de la microélectronique a connu une croissance exceptionnelle tant en termes de taille que de fonctionnalités. Des améliorations technologiques constantes ont été réalisées grâce à la miniaturisation, apportant à la fois des gains continus de performance et d'efficacité. L'industrie est aujourd'hui structurée autour de ces gains escomptés, mais s'il y avait initialement « beaucoup de place en bas » (pour citer Feynman) pour la miniaturisation, ce n'est plus le cas, et la poursuite de l'augmentation de la densité des circuits intégrés entraînera maintenant davantage de changements de géométrie, puisque les **Fin FETs (FinFETs)** sont désormais courants dans la plupart des noeuds avancés, et que des nanofils verticaux[Poi22] sont envisagés.

Une autre voie possible pour accroître les performances et l'efficacité énergétique n'implique pas d'augmenter la densité, mais plutôt de permettre de nouvelles fonctionnalités à un niveau de miniaturisation similaire. C'est le cas des modifications apportées aux dispositifs tels que les transistors **silicium entièrement appauvri sur isolant (FDSOI, Fully Depleted Silicon on Insulator)** et **transistors à effet de champ ferroélectriques**, mais aussi des modifications apportées aux architectures informatiques, qui peuvent apporter des gains de performance tangibles.

Outre les considérations économiques (les nouvelles technologies stimulent les ventes en rendant obsolètes les générations précédentes d'appareils), les gains d'efficacité énergétique sont importants pour compenser l'empreinte écologique et énergétique croissante des appareils électroniques. Ces gains sont compensés dans une certaine mesure par un effet de rebond, car des appareils moins chers, plus puissants et plus économies en énergie permettent de nouveaux cas d'utilisation. Cela entraîne toutefois une diversification des utilisations possibles qui est difficilement quantifiable, et rend la technologie financièrement plus abordable.

Dans cette introduction, les tendances actuelles en microélectronique sont résumées, en soulignant pourquoi l'approche historique n'est plus suffisante pour l'obtention de gains d'efficacité. De nouveaux cas d'utilisation tels que l'**Internet des Objets (IoT, Internet of Things)** et le **calcul de périphérie** sont décrits, ainsi qu'une technologie émergente spécifique, basée sur les **HfZrO<sub>2</sub>** ferroélectriques, ainsi que le projet européen **3εFERRO** dont ce travail fait partie.

<sup>1</sup> miroirs disponibles à <https://thesis.mayeul.net> <https://mayeulc.gitlab.io/thesis>, <https://thesis.mayeul.cantan.eu> et <https://mayeulc.github.io/thesis>

### 1.2.1 Internet des Objets et calcul de périphérie

#### Internet des Objets

L'**IoT** comprend une multitude d'appareils et de catégories d'appareils. Il s'agit généralement de capteurs mesurant des quantités physiques telles que la température, l'humidité ou la pression atmosphérique, ou des valeurs plus spécifiques telles que la consommation énergétique, le nombre de voitures dans un parking, les capteurs de mouvement dans le cadre d'un système d'alarme, etc. Des dispositifs plus complexes peuvent également être considérés comme faisant partie de l'**IoT**, tels que les voitures modernes connectées à Internet, ou les dispositifs « intelligents » de plus en plus courants dans les maisons, tels que les thermostats, bouilloires, lumières, rideaux, litières pour chats, etc... connectés au réseau. Ces dispositifs comprennent parfois des actionneurs ainsi que des capteurs, dont certains peuvent être essentiels à la sécurité des personnes, comme une barrière contrôlant l'accès à une rampe de sortie d'urgence sur une autoroute.

L'**IoT** est un marché en pleine expansion, car la collecte de données et l'accès à des données supplémentaires depuis Internet permettent des comportements beaucoup plus complexes. Par exemple, l'utilisation de capteurs de température et d'humidité du sol peuvent aider à surveiller les cultures ; et la connexion d'un système d'irrigation aux prévisions météorologiques peut permettre d'économiser de l'eau. Cependant, contrairement au **cloud**, qui est composé de serveurs puissants et coûteux situés dans des centres de données connectés à un réseau électrique, l'**IoT** est généralement bon marché, non réutilisable, avec des contraintes d'énergie et de connectivité. Le coût et l'efficacité énergétique signifient que les dispositifs **IoT** ont généralement des quantités très limitées de mémoire et de puissance de calcul. En effet, qu'il s'agisse d'un capteur d'humidité placé au milieu d'un champ durant plusieurs années, d'un capteur de pression sur la jante d'une roue de voiture ou d'un capteur d'ouverture/fermeture en haut d'une fenêtre, l'alimentation électrique de ces dispositifs est souvent difficile, ce qui conduit à un grand nombre de dispositifs fonctionnant sur batterie, parfois complétés par des mécanismes de récupération d'énergie : panneaux solaires, triboélectricité ou collecteurs d'énergie vibratoire, modules peltier ou thermoélectriques pour récupérer la chaleur perdue, etc. Cela signifie également que ces appareils s'appuient souvent sur une connexion sans fil pour transmettre des données, ce qui nécessite une quantité d'énergie relativement importante : selon sa fiche technique [Esp22], un ESP8266EX très répandu consomme généralement environ 50 mW avec son modem radio éteint, tandis que la transmission de données à 15 dBm utilise un ordre de grandeur supplémentaire d'énergie. Lorsque son processeur est éteint, cet appareil ne consomme que 0.5 mW à 20 mW.

#### Calcul de périphérie

L'**IoT** utilise largement le **cloud** comme source et destination de données. Toutefois, comme indiqué précédemment, la transmission de données a un coût énergétique non négligeable pour les appareils alimentés par batterie. Cela devient également un problème de bande passante lorsque les données atteignent les serveurs : les coûts de transit sur Internet peuvent être considérables, et les coûts de traitement augmentent avec la quantité de données.

L'**calcul de périphérie** vise à relocaliser certaines tâches de traitement en dehors du **cloud**, à sa périphérie. Il s'agit du traitement de données qui est trop intensif pour être effectué sur les appareils **IoT** eux-mêmes en raison de contraintes de ressources, mais pour lequel l'application d'une certaine quantité de prétraitement peut réduire la latence et la bande passante envoyées au **cloud**.

En pratique, le traitement des données au plus près de la source permet généralement de réaliser des gains d'efficacité. Par exemple, dans un système de vidéosurveillance, une caméra sans fil (dispositif **IoT**) peut éviter de transmettre des données lorsqu'aucun mouvement n'est détecté, et compresser le flux vidéo avant de l'envoyer pour économiser de l'énergie lors de la transmission. Ce flux serait ensuite envoyé à un dispositif intermédiaire plus puissant (*dispositif de périphérie*) pour un traitement ultérieur. Il peut s'agir d'une tâche de reconnaissance d'images, d'identification d'un renard dans un élevage de poulets ou d'une personne armée dans une foule. Ce dispositif périphérique effectue donc des tâches de traitement relativement intensives pour pré-filtrer les données avant de les envoyer à des serveurs distants

pour un traitement ultérieur. Dans l'exemple ci-dessus, il peut s'agir d'archiver la vidéo ou de la transmettre à un autre appareil.

Un autre exemple est un assistant vocal pouvant effectuer une reconnaissance vocale locale basique, pour répondre plus rapidement aux commandes, mais aussi pour transmettre du texte plutôt que de la voix au **cloud**; cela présente également des avantages en termes de disponibilité et de respect de la vie privée.

### 1.2.2 Fin de la mise à l'échelle de Dennard et de la loi de Moore

#### Loi de Moore

La loi de Moore a été formulée en 1965[Moo65] par Gordon Moore (cofondateur d'Intel, 1929–2023), selon laquelle le nombre d'élément (c'est-à-dire de transistors) sur un circuit intégré doublait tous les deux ans pour les puces les plus économiques (au coût le plus faible par élément). Cette observation est généralement résumée par un doublement de densité de transistor tous les deux ans, et s'est maintenue bien plus longtemps qu'initiallement prévu. Cela est en partie dû au fait que l'industrie l'a utilisée comme feuille de route pour le développement, comprenant les investissements dans de nouvelles usines, les dépenses de R&D et la planification des produits.

#### Mise à l'échelle de Dennard

Après la transition de l'industrie vers les transistors **Transistor à Effet de Champ Méta-Oxide-Semiconducteur (MOSFET)**, la mise à l'échelle de Dennard a été identifiée en 1974[Den+74] comme un moyen faisable de continuer à augmenter la densité de transistors sur les puces électroniques, en réduisant leurs dimensions tel que spécifié dans le **tableau 1.1**. Ces valeurs sont établies en réduisant la taille des transistors tout en maintenant le champ électrique constant.

| Paramètre du circuit ou dispositif               | Facteur d'échelle |

|--------------------------------------------------|-------------------|

| Dimensions des dispositifs $t_{ox}$ , $L$ , $W$  | $1/\kappa$        |

| Concentration en dopants $N_a$                   | $\kappa$          |

| Tension $V$                                      | $1/\kappa$        |

| Courant $I$                                      | $1/\kappa$        |

| Délai par circuit $V \cdot C/I$                  | $1/\kappa$        |

| Dissipation de puissance par circuit $V \cdot I$ | $1/\kappa^2$      |

| Densité de puissance $V \cdot I/A$               | 1                 |

TAB. 1.1 : Paramètres de mise à l'échelle de Dennard et impact sur les performances, d'après [Den+74]. La densité de puissance est maintenue constante.

Cette méthode de mise à l'échelle a conduit à une constante augmentation de la densité au cours des années suivantes, la période de 1980 à 1995 étant surnommée l'ère de la « mise à l'échelle facile » (happy scaling). Grâce à l'amélioration des méthodes de fabrication, les dimensions des dispositifs et des circuits ont pu être réduites à un rythme régulier. Cette réduction de la taille des composants et des interconnexions a permis de diminuer les capacités de grille, augmentant ainsi simultanément la fréquence maximale de fonctionnement et l'efficacité énergétique en réduisant les pertes par commutation.

Afin de respecter la trajectoire de la loi de Moore,  $\kappa$  a été choisi pour réduire de moitié la surface des transistors  $A \approx L \cdot W$  à chaque génération :  $1/\kappa^2 = 1/2 \implies \kappa = \sqrt{2} \approx 1.4$ [Boh07], approximativement tous les deux ans.

#### Conséquences d'une « mise à l'échelle facile »

Les gains de performance constants eurent un effet profond sur l'ensemble de l'industrie : il était souvent possible de réutiliser des modèles de puces antérieurement conçues, de les redimensionner, puis de les fabriquer avec le processus amélioré afin d'obtenir des gains de performance. En outre, les algorithmes conçus pour des processeurs non spécialisés pouvaient

également bénéficier de ces gains de performance, à condition que la rétrocompatibilité soit maintenue d'une génération de puces à l'autre. Le maintien de la rétrocompatibilité avec les précédentes générations de matériel et de logiciels s'est avéré bénéfique, permettant des améliorations itératives et répercutant l'impact des investissements sur plusieurs générations.

En conséquence, le développement des architectures de processeurs non spécialisées et les algorithmes, outils et compilateurs associés ont dépassé celui du matériel à usage spécifique : dans certains cas, des circuits **ASICs** et architectures de processeurs personnalisées pouvaient offrir des avantages en termes de performances et d'efficacité par rapport aux implémentations sur **processeur (CPU, Central Processing Unit)**. Cependant, la longue et coûteuse phase de conception combinée à l'augmentation constante des performances des **CPU** pouvait rendre ces derniers aussi performants qu'une solution spécifique avant que celle-ci ne soit disponible.

Notre écosystème matériel et logiciel actuel doit être observé sous cette perspective historique, et ce travail reflète le récent regain d'intérêt pour les approches alternatives.

### Fin de la mise à l'échelle de Dennard

Il est impossible de continuer indéfiniment la mise à l'échelle de Dennard. En effet, des limites techniques, de fabrication et physiques interviennent : les tensions ne peuvent pas descendre en dessous d'un certain niveau, car cela dégrade le rapport signal/bruit des niveaux logiques et de leur amplification par les transistors. Les concentrations de dopants deviennent difficiles à augmenter à mesure que la taille diminue, ce qui entraîne des problèmes tels qu'une distribution atomique inégale et un effet tunnel direct de bande à bande à travers les jonctions PN (source et drain du transistor)[Boh07]. Les dimensions ont également des limites fondamentales, car le courant d'effet tunnel devient non négligeable en dessous d'une certaine taille (en fonction de la tension et d'autres facteurs, environ 20 nm).

Alors que les dimensions de fabrications descendaient sous 65 nm, les courants de fuite continuaient d'augmenter, particulièrement au niveau des isolants de grille, alors d'une épaisseur de 1.2 nm, soit environ cinq couches atomiques de SiO<sub>2</sub> en 2005[Boh07]. Cela conduit à l'introduction de diélectriques « **high-k** » afin de conserver l'intensité du champ électrique dans le canal du transistor malgré l'utilisation d'oxydes de grille plus épais. Cela permet de réduire le courant de fuite, mais rompu avec la mise à l'échelle de Dennard. Par la suite, la mise à l'échelle à champ constant rencontra davantage de problèmes qui nécessitèrent de repenser l'approche.

La fin de la mise à l'échelle de Dennard eut un effet notable sur la dissipation de puissance des circuits intégrés : les tensions ne pouvant plus être abaissées davantage, et les courants de fuite augmentant, la densité de puissance ne pouvait plus rester constante. Cela entraîna une augmentation considérable de la consommation d'énergie des puces et processeurs modernes, bien que l'efficacité énergétique puisse encore être améliorée grâce à l'augmentation des performances. Les courants de fuite peuvent également être atténués en désactivant l'alimentation des zones inutilisées des puces, une approche intitulée « silicium sombre » (dark silicon).

### Fin de la loi de Moore

Bien que la réduction des dimensions des transistors put continuer plusieurs années après la fin de la mise à l'échelle de Dennard, les limites de la technologie planaire **MOSFET** étaient proches. En l'absence d'une feuille de route claire pour la mise à l'échelle, les investissements nécessaires pour suivre la feuille de route tracée par Moore ont continué à croître rapidement, accélérant la consolidation de l'industrie des semi-conducteurs.

Plus récemment, les augmentations de densité n'ont pas été à la hauteur des prédictions de Moore et ont été obtenues grâce à des modifications plus importantes de l'architecture des **transistor à effet de champ (FET, Field Effect Transistor)**, avec la généralisation de **FinFET** et le développement de **FET à grille englobante (GAAFET, Gate-All-Around FET)** et de **FETs à nanofils verticaux**. Ces modifications permettent d'augmenter la densité de transistors en exploitant la dimension verticale, sans réduction majeure de dimensions.

L'augmentation de la taille des puces est un autre moyen de continuer à augmenter le nombre d'éléments par puce, avec des progrès récemment effectués dans le domaine des puces à l'échelle de la plaque. Toutefois, il est peu probable que cela compense l'augmentation des coûts des dernières générations de procédés de fabrication de semi-conducteurs, qui reflète les investissements importants nécessaires à l'augmentation continue de la densité de transistors.

Les futures améliorations de performance pourraient continuer à provenir de l'augmentation de la densité et du nombre de structures (à une cadence ralentie), mais également de nouvelles architectures de systèmes et de nouveaux dispositifs, possiblement non électriques (photonique, stockage moléculaire). Diverses appellations ont été utilisées pour décrire ces approches respectives, notamment « plus de Moore » et « plus que Moore ».

L'amélioration de l'efficacité énergétique est peut-être un défi plus difficile à relever que l'augmentation de densité, sans l'assistance de la mise à l'échelle de Dennard, qui s'effectue à densité de puissance constante. Les problèmes de dissipation thermiques sont aggravés par l'abandon des transistors planaires, qui permettaient de maximiser la surface de contact avec le substrat de silicium.

Reflétant ce changement d'orientation, l'industrie cherche à se réinventer, et étudie de nombreuses technologies émergentes, y compris certaines pistes abandonnées durant l'ère de la « mise à l'échelle heureuse ». La cadence réduite de l'amélioration des performances des transistors conventionnels pourrait ainsi permettre aux alternatives de rattraper leur retard en termes de performances. Ce travail présente l'un de ces axes de recherche sur les matériaux ferroélectriques, afin d'apporter de nouvelles fonctionnalités aux technologies de semi-conducteurs existantes.

L'[International Technology Roadmap for Semiconductors \(ITRS\)](#), qui coordonne le développement des prochaines générations de dispositifs à base de silicium dans l'industrie, a également illustré cette tendance en 2016, changeant de nom pour l'[International Roadmap for Devices and Systems \(IRDS\)](#). Les rapports de cet organisme offrent une vue d'ensemble des technologies en cours de développement et de leurs applications potentielles[[IRDS22](#)].

### 1.2.3 Architecture Von Neumann

Les architectures d'ordinateurs sont aujourd'hui majoritairement conçus autour du concept de programmes stockés : en stockant les programmes dans la mémoire de travail, ceux-ci peuvent facilement être chargés et modifiés, ainsi que copiés et transférés. Cela rend nos ordinateurs bien plus polyvalents, car il n'est ainsi pas nécessaire de leur apporter de modifications physiques afin d'exécuter une nouvelle fonction, contrairement aux premières architectures.

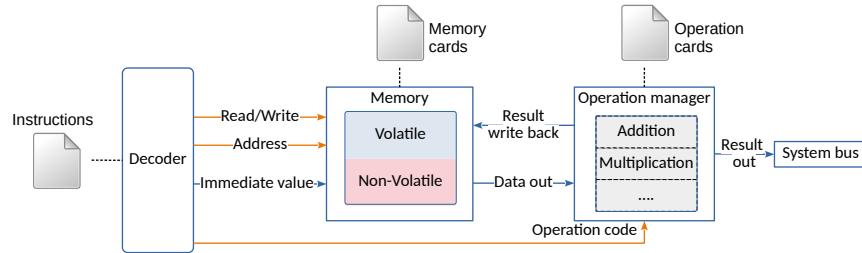

L'une des architectures informatiques suivant ce paradigme les plus utilisées est l'architecture Von Neumann, illustrée par la [figure 1.1](#), et ses dérivées[[Paw22](#)]. Portant le nom de John von Neumann, celle-ci lit instructions et données depuis la même mémoire, via d'un bus mémoire. Cette architecture peut être généralisée en plaçant plusieurs périphériques, y compris des dispositifs d'[Entrée/Sortie \(I/O, Input/Output\)](#), sur ce bus mémoire (ou bus système) à des adresses préalablement définies, et communiquer avec grâce à la même interface composée d'un bus de données et du bus d'adresses, effectuant des opérations de lecture et d'écriture. Cette généralisation a permis de rendre les architectures modernes très modulaires, utilisant une abstraction commune pour la plupart des cas d'usage. Les « périphériques » tels que les adaptateurs d'[I/O](#) supplémentaires, les coprocesseurs ou les dispositifs spécialisés peuvent communiquer avec le [CPU](#) et le programme qui s'y exécute en s'interfaisant avec ce bus mémoire unifié.

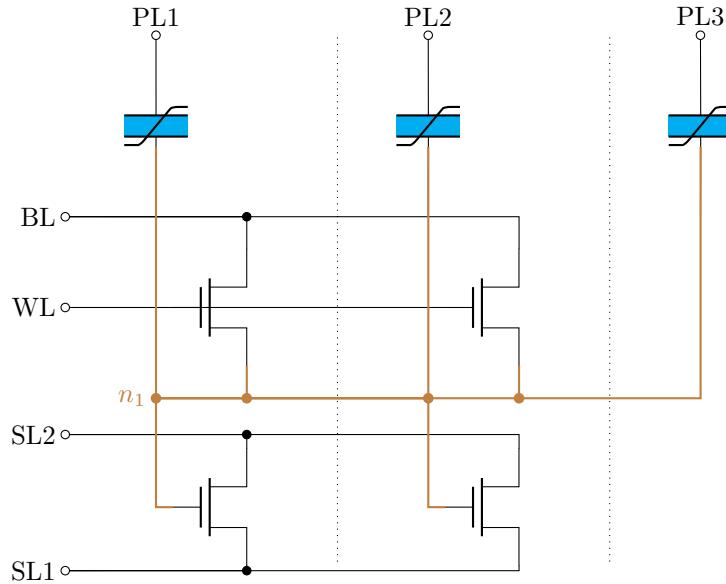

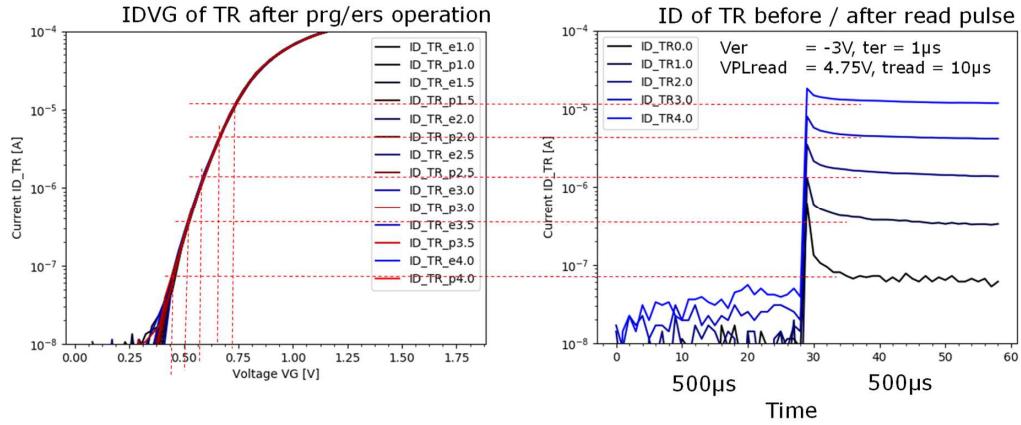

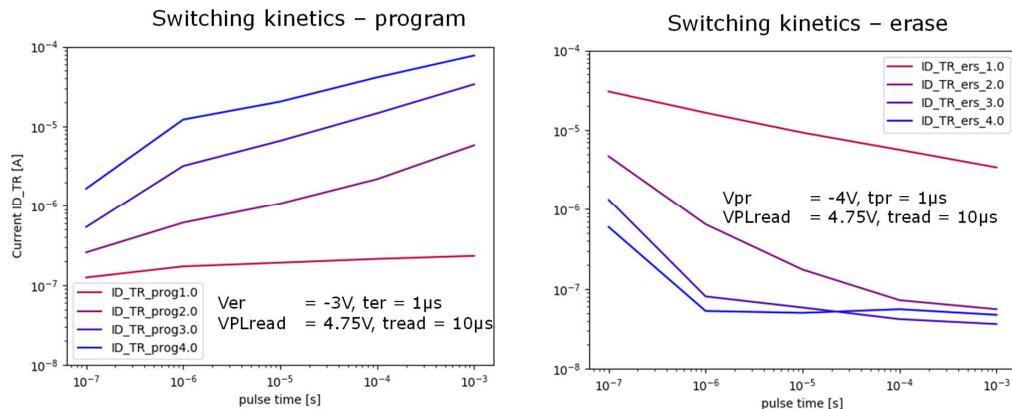

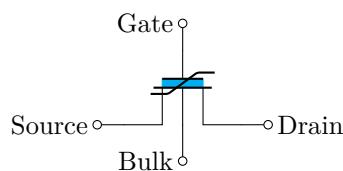

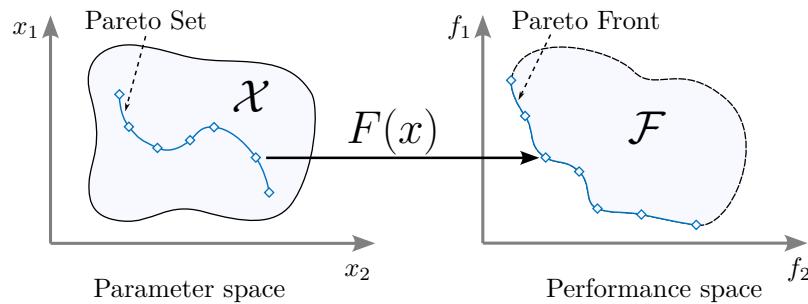

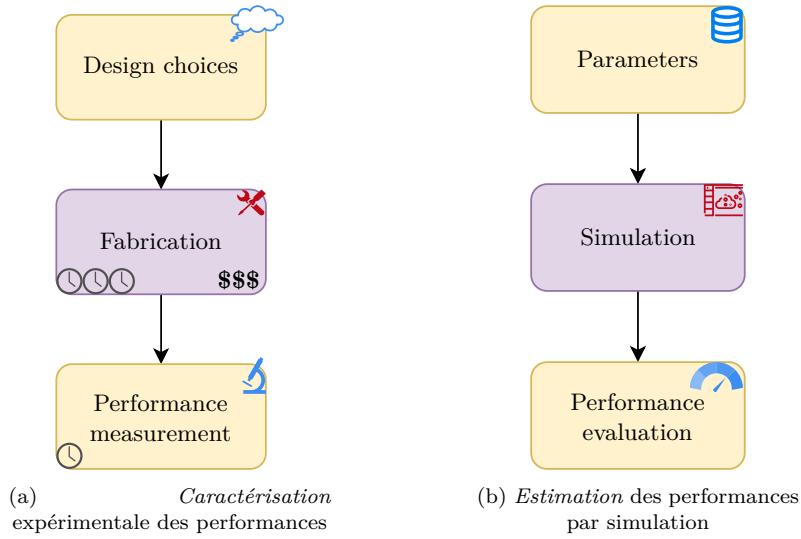

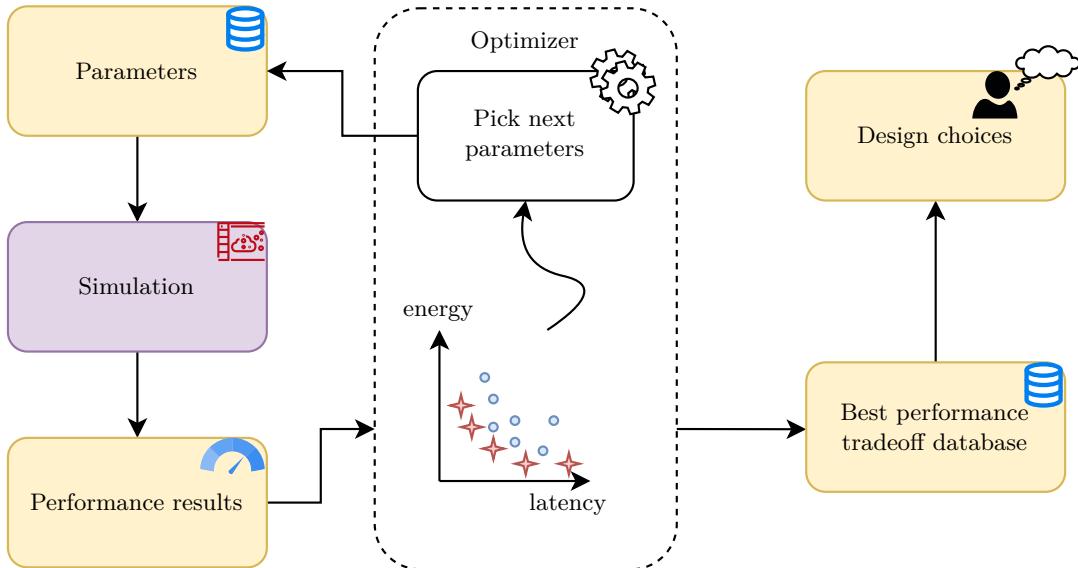

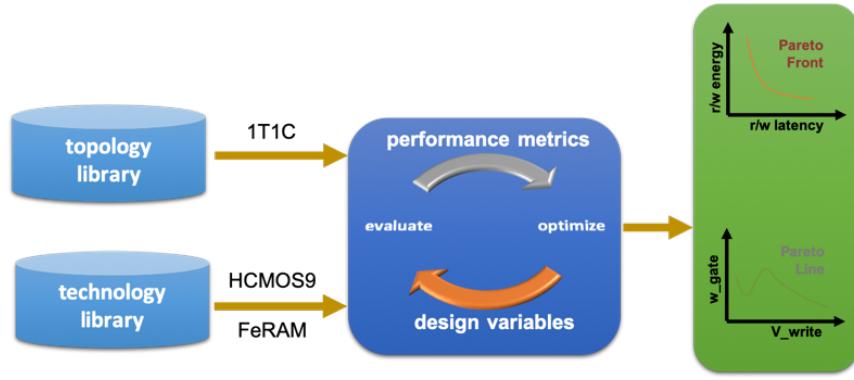

### 1.2.4 Goulot d'étranglement de Von Neumann