$N^{\circ}$  d'ordre NNT : 2023ECDL0026

# THÈSE de DOCTORAT DE L'ÉCOLE CENTRALE DE LYON opérée au sein de l'Université de Lyon

École Doctorale n°160 Électronique Électrotechnique et Automatique (EEA)

Discipline : Électronique, Micro et Nanoélectronique, Optique et Laser

Soutenue publiquement le 5 juillet 2023, par :

#### Mayeul Cantan

## Energy-Efficient Computing with Integrated Ferroelectrics for Embedded and Edge Devices

#### Devant le jury composé de :

| Maneux, Cristell    | Professeur des Universités <sup>a</sup> | Université de Bordeaux / IMS Bordeaux                                   | Présidente            |

|---------------------|-----------------------------------------|-------------------------------------------------------------------------|-----------------------|

| Niemier, Michael    | Full Professor                          | University of Notre Dame, Indiana, USA Aix-Marseille Université / IM2NP | Rapporteur            |

| Portal, Jean-Michel | Professeur des Universités <sup>a</sup> |                                                                         | Rapporteur            |

| O'Connor, Ian       | Professeur des Universités <sup>a</sup> | École Centrale de Lyon / INL                                            | Directeur de thèse    |

| Deleruyelle, Damien | Professeur des Universités <sup>a</sup> | INSA Lyon / INL                                                         | Co-directeur de thèse |

| Marchand, Cédric    | Maître de Conférences <sup>a</sup>      | École Centrale de Lyon / INL                                            | Co-directeur de thèse |

| Slesazeck, Stefan   | Senior Researcher                       | NaMLab, Dresden, Allemagne                                              | Invité                |

| Giraud, Bastien     | Ingénieur Chercheur                     | CEA-LIST                                                                | Invité                |

$a63^{\rm ème}$  section

#### UNIVERSITÉ DE LYON

## Abstract

École Centrale de Lyon Department Name

PhD

## Energy-Efficient Computing with Integrated Ferroelectrics for Embedded and Edge Devices

by Mayeul Cantan

Ferroelectric materials are gaining traction in integrated circuits, notably thanks to the introduction of Hafnium-Zirconium Oxides, which are compatible with state-of-the-art semiconductor materials and manufacturing technologies. Their ferroelectric properties, combined with regular CMOS technology, enable interesting new circuit architectures. Bringing Non-Volatile Memory technology closer to compute elements unlocks opportunities for higher power efficiency by reducing data transfers, lowering static power consumption, and enabling normally-off computing schemes.

In this thesis, ferroelectric materials are approached from a circuit design perspective, providing a basic understanding of their properties and modeling approaches. Multiple circuit architectures enabled by ferroelectric materials are also presented, both with Back-End of Line and Ferroelectric Field-Effect Transistor (FeFET) technologies, and electrical characterization results where available. Finally, projected performance figures are extracted, to allow comparison with more mature technologies, both at the circuit and system level, through Design-Space Exploration (DSE) techniques and a custom system-level performance evaluation framework.

Obtained results include novel circuit designs, some of which were fabricated with 130 nm and 28 nm technology, DSE simulation results for metrics such as memory window and energy consumption, as well as multiple software tools created during the project.

## Acknowledgments

This document may bear my name on the first page, but I wouldn't have been able to complete it without the direct and indirect contributions of the people who helped me along this journey, and those that encouraged me. I could not include everyone on this page, but to those whose name isn't written down: thank you for your help and support over the course of my PhD.

I am first and foremost grateful to my supervisor Ian O'Connor, who accompanied me during this thesis, providing support and advice, and being responsive as I faced difficulties. My co-supervisors Cédric Marchand and Damien Deleruyelle were of great help for discussing simulations and physics of ferroelectric devices; and for the review of this document, as well as Damien's more direct contributions to subsection 2.2.2.

My thanks extend to my esteemed colleagues that I also call friends for their support over the years: Clément Zrounba and Arnaud Poittevin helped me with the layout of MAD200 designs discussed in chapter 3, and partook in numerous fruitful scientific discussions. Etienne Dupuis, for his contagious motivation and his open heart, Adil Brik, Lucien Del Bosque, followed by the next generations of PhD students were always ready to help, whether it was work-related or with personal matters. This resulted in a welcoming work environment, where I made some of my fondest memories.

For their help and support, I would like to thank the rest of my team members at INL, including Alberto Bosio, for his help with design synthesis in the context of the image filter presented in section 4.6. Other 3eFERRO project members were also of great help, including at INL, where Jordan Bouaziz and other members of the Materials team, including Ingrid Cañero Infante, Bertrand Vilquin and Pedro Rojo Romeo, patiently taught me over and over the physics and fabrication aspects of ferroelectric materials. I also owe some of my understanding of ferroelectrics to NaMLab personnel, especially Stefan Slesazeck and Evelyn Breyer, who carried out much of the design and implementation work of the convolutional image filter discussed in section 4.6. Evelyn was instrumental to the work presented in this document by providing the "Preisach" ferroelectric simulation model used for most simulations, though the first modeling discussions and experimental data I obtained were courtesy of Carlotta Gastaldi from EPFL, which enabled my first "Landau"-based simulations.

For successively helping me develop the system-level benchmarking platform described in section 5.4, I would like to thank in chronological order master students Pierre-Etienne Polet and Luca Mozzone, and postdoctoral researcher Marcello Traiolla. They successively provided the main development effort for implementing my designs, and provided great feedback on them. Their documentation efforts were tremendously helpful while writing this section.

For their support, and constant encouragements, I would also like to thank my family, including my parents and siblings, who constantly teased me about the progress on my manuscript, while doing their best to support me during these trying times. Writing this manuscript was not an easy task, neither for me nor the people surrounding me, so I am grateful to Liz, for her patience, understanding and support.

I found unconditional support among my friends as well, who I have not forgotten despite seeing them less often, and whom I miss after all that time spent working isolated. You will recognize yourselves, and I hope to see you again soon! I particularly want to thank Claire Segovia for taking some of her time to help me work through the early stages of writing this manuscript, and helping me overcome writer's block and reject distractions, which was extremely helpful.

Less conventionally, I would also like to thank Romano Giannetti, the maintainer of the circuitikz circuit illustration library that I have used extensively throughout this document, for answering my request to create ferroelectric capacitors and transistors symbols<sup>1</sup>. These thanks extend to the maintainers of the countless open source tools used over the course of this PhD, as well as Laurent Carrel for administrating our local computing resources.

Lastly, I am grateful to the European Commission for funding interesting and relevant projects, which enabled me to conduct this work as part of the  $3\varepsilon FERRO$  project that received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement N°780302.

<sup>1</sup>https://github.com/circuitikz/circuitikz/issues/515

# Contents

| A | bstra        | ct                        |                                                              | 3               |

|---|--------------|---------------------------|--------------------------------------------------------------|-----------------|

| A | ckno         | wledgn                    | nents                                                        | 5               |

| 1 | Introduction |                           |                                                              |                 |

|   | 1.1          |                           | this document                                                | 15<br>15        |

|   |              | 1.1.1                     | License                                                      | 15              |

|   |              | 1.1.2                     | Internal links and color code                                | 15              |

|   |              | 1.1.3                     | Document source, errata and supplementary material           | 16              |

|   |              | 1.1.4                     | Aim of this document                                         | 16              |

|   | 1.2          |                           | xt                                                           | 16              |

|   | 1.2          | 1.2.1                     | Internet of Things and edge computing                        | 16              |

|   |              | 1.2.1                     |                                                              | 16              |

|   |              |                           | Internet of Things                                           | 17              |

|   |              | 1.2.2                     | Edge computing                                               | 17              |

|   |              | 1.2.2                     | The demise of Dennard scaling and Moore's law                |                 |

|   |              |                           | Moore's Law                                                  | 17              |

|   |              |                           | Dennard scaling                                              | 17              |

|   |              |                           | "Happy scaling" consequences                                 | 18              |

|   |              |                           | End of Dennard scaling                                       | 18              |

|   |              |                           | End of Moore's Law                                           | 18              |

|   |              | 1.2.3                     | Von Neumann Architecture                                     | 19              |

|   |              | 1.2.4                     | Von Neumann Bottleneck                                       | 19              |

|   |              | 1.2.5                     | Ferroelectric HfZrO <sub>2</sub>                             | 20              |

|   |              | 1.2.6                     | Conclusion                                                   | 21              |

|   | 1.3          | $3\varepsilon \text{FEF}$ | RRO European project                                         | 21              |

|   |              | 1.3.1                     | Project partners                                             | 21              |

|   |              | 1.3.2                     | Project Goals                                                | 22              |

|   |              |                           | Achievements                                                 | 22              |

|   |              |                           | Contributions                                                | 22              |

| 2 | Fer          | roelect                   | rics: behavior and modeling                                  | 23              |

|   | 2.1          | Ferroe                    | electricity                                                  | 23              |

|   |              | 2.1.1                     | Ferroelectric crystals                                       | 23              |

|   |              |                           | Coercive field                                               | 24              |

|   |              |                           | Polycrystals and domains                                     | 24              |

|   |              |                           | Note on the nomenclature used for write and erase operations | 27              |

|   |              | 2.1.2                     | <i>P-V</i> curve                                             | 27              |

|   |              | 2.1.3                     | Relationship with capacitance and paraelectricity            | 27              |

|   |              | 2.1.0                     | Charge screening and depolarization field                    | 29              |

|   |              |                           | Ferroelectric Tunnel Junction                                | 30              |

|   |              | 2.1.4                     | PUND measurements                                            | 30              |

|   | 2.2          | Model                     |                                                              | 34              |

|   | 2.2          | 2.2.1                     | Landau model                                                 | 34              |

|   |              | 4.4.1                     |                                                              | $\frac{34}{34}$ |

|   |              |                           | Description                                                  |                 |

|   |              |                           | Expression                                                   | 35              |

|   |              |                           | Usage                                                        | 36              |

|   |              |                           | Fitting                                                      | 36              |

|   |              | 0.0.0                     | Conclusion                                                   | 37<br>37        |

|   |              | 999                       | Program model                                                | .7.7            |

|   |     | Acknowledgements                                               | 37         |

|---|-----|----------------------------------------------------------------|------------|

|   |     | Hysterons                                                      |            |

|   |     | Cumulative hysteron behavior                                   |            |

|   |     | Limitations                                                    |            |

|   |     | 2.2.3 Simplified model for large-scale simulation              |            |

|   | 2.3 |                                                                |            |

|   | 2.0 | 2.3.1 Regular capacitor                                        |            |

|   |     |                                                                |            |

|   |     | 2.3.2 Non-volatility                                           |            |

|   |     | 2.3.3 Negative capacitance                                     |            |

|   | 2.4 |                                                                |            |

|   |     | 2.4.1 FeFET Devices                                            |            |

|   |     | Drawbacks                                                      | 46         |

|   |     | 2.4.2 Gate stacks                                              | 46         |

|   |     | 2.4.3 Modeling                                                 | 47         |

|   | 2.5 | 5 State-of-the-art on ferroelectric circuits                   | 47         |

|   |     | 2.5.1 Ferroelectric Hafnia                                     | 47         |

|   |     | Modeling                                                       | 48         |

|   |     | 2.5.2 Ferroelectric Capacitors and Back-End of Line circuit    |            |

|   |     | 2.5.3 Ferroelectric Field-Effect Transistors-based circuit des |            |

|   |     | P-channel Ferroelectric Field-Effect Transistors               | <u> </u>   |

|   |     | 2.5.4 Comparison with other Non-Volatile Memories              |            |

|   |     |                                                                |            |

|   |     | 2.5.5 Design-Space Exploration                                 |            |

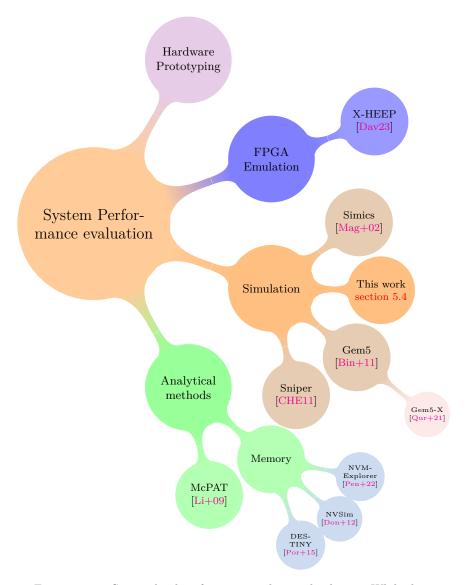

|   |     | 2.5.6 System-level performance evaluation                      |            |

|   |     | Hardware prototyping                                           |            |

|   |     | FPGA-based emulators                                           |            |

|   |     | Software simulators                                            |            |

|   |     | Compiler support and code instrumentation                      | 52         |

|   |     |                                                                |            |

| 3 |     | erroelectric capacitors-based designs                          | 53         |

|   | 3.1 |                                                                |            |

|   |     | 3.1.1 Back-End of Line technology                              |            |

|   |     | 3.1.2 MAD200 process                                           |            |

|   | 3.2 | 2 1T1C memory bitcell                                          | 54         |

|   |     | 3.2.1 Operation                                                | 55         |

|   |     | Bitcell selection and programming                              | 55         |

|   |     | Bitcell readout                                                | 57         |

|   |     | Multi-level memory                                             |            |

|   |     | 3.2.2 Simulation                                               | <b>~</b> ^ |

|   |     | MAD200-based simulations                                       |            |

|   | 3.3 |                                                                |            |

|   |     | 3.3.1 Description                                              |            |

|   |     | 3.3.2 Design                                                   |            |

|   |     | Capacitance matching                                           |            |

|   |     | 3.3.3 Characterization                                         |            |

|   |     |                                                                |            |

|   |     | Protocol and results                                           |            |

|   | 0.4 | 3.3.4 Extension to multi-transistor circuits                   |            |

|   | 3.4 |                                                                |            |

|   |     | 3.4.1 Description                                              |            |

|   |     | Ternary Content-Addressable Memory                             |            |

|   |     | Operating principle                                            |            |

|   |     | Limitations                                                    | 67         |

|   |     | 3.4.2 Design                                                   | 67         |

|   | 3.5 |                                                                |            |

|   |     | 3.5.1 Description                                              |            |

|   |     | Programming                                                    |            |

|   |     | Reading as FTJ – Non-destructive read                          |            |

|   |     | Reading as DRAM, or 1T1C – Destructive read                    |            |

|   |     | Reading as FeFET – Non-destructive read                        |            |

|   |     | reading as refer to 1 - fron-destructive read                  |            |

|   |     |        | 2T-nC                                                            |

|---|-----|--------|------------------------------------------------------------------|

|   |     |        | Destructive TCAM emulation                                       |

|   |     | 3.5.2  | Design                                                           |

|   |     |        | Capacitance matching for DRAM operation with destructive read 71 |

|   |     |        | 2T-nC                                                            |

|   |     | 3.5.3  | Characterization results                                         |

|   |     |        | Reference $I_{DS}$ — $V_{GS}$ plot for $Q_R$                     |

|   |     |        | Characterization protocol                                        |

|   |     |        | Results and interpretation                                       |

|   |     |        | Switching dynamics investigation                                 |

|   | 3.6 | Concl  | sion                                                             |

|   | 5.0 | 3.6.1  | 1T1C memory bitcell                                              |

|   |     | 0.0    |                                                                  |

|   |     | 3.6.2  | Back-End of Line FeFET-like structure                            |

|   |     | 3.6.3  | Destructive-read TCAM                                            |

|   |     | 3.6.4  | 2T1C                                                             |

|   |     |        |                                                                  |

| 4 |     |        | ric transistor-based designs 79                                  |

|   | 4.1 |        | uction to FeFET circuits                                         |

|   |     | 4.1.1  | Programming the ferroelectric oxide                              |

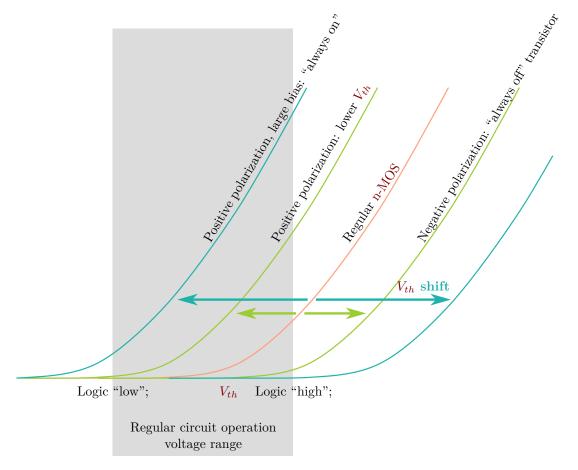

|   |     | 4.1.2  | $V_{th}$ shifting                                                |

|   |     |        | Analog $V_{th}$ shift control                                    |

|   |     |        | Dual-state $V_{th}$ shift control                                |

|   |     | 4.1.3  | Comparison with CMOS-based logic                                 |

|   |     |        | Advantages compared to CMOS-based logic 82                       |

|   |     |        | Deficiencies compared to CMOS-based logic 83                     |

|   |     |        | Technology process and p-FeFET availability                      |

|   | 4.2 | 1T-Fel | FET memory                                                       |

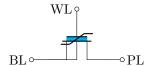

|   |     | 4.2.1  | Operating principle                                              |

|   |     |        | Read operation                                                   |

|   |     |        | Write operation                                                  |

|   |     | 4.2.2  | Comparison with other floating-gate transistor memories          |

|   |     | 4.2.3  | Possible hybrid operation mode                                   |

|   | 4.3 |        | resistance circuits                                              |

|   | 4.0 | 4.3.1  | Complementary logic with p-FeFET                                 |

|   |     | 4.3.1  |                                                                  |

|   |     |        |                                                                  |

|   |     | 4.3.3  | Dynamic logic                                                    |

|   |     | 4.0.4  | Hybrid dynamic logic with CMOS stages                            |

|   |     | 4.3.4  | Pass-transistor logic                                            |

|   |     |        | FeFET-based pass-transistors                                     |

|   | 4.4 |        | olatile FeFET-based logic gates                                  |

|   |     | 4.4.1  | NV-NAND2                                                         |

|   |     | 4.4.2  | NV-AND2                                                          |

|   |     | 4.4.3  | NV-XOR2                                                          |

|   | 4.5 | FeFET  | Is as add-on technology    91                                    |

|   |     | 4.5.1  | Black & Das memory cell as a checkpointing mechanism 91          |

|   | 4.6 | Convo  | lutional Image Filter with FeFET-based Logic-in-Memory 92        |

|   |     | 4.6.1  | Choice of a convolutional image filter                           |

|   |     |        | Convolution operation in one dimension                           |

|   |     |        | Convolution of a two-dimensional image                           |

|   |     |        | Required post-processing                                         |

|   |     | 4.6.2  | Filter architecture                                              |

|   |     | 1.0.2  | Intermediate samples                                             |

|   |     |        | Alternate scan-chain                                             |

|   |     |        |                                                                  |

|   |     | 169    | 1                                                                |

|   |     | 4.6.3  | v i                                                              |

|   |     |        | Multiplier circuit, adder circuit                                |

|   |     |        | Ripple-Carry Adder                                               |

|   |     |        | Pipelined architecture                                           |

|          |                |         | 0 1 0 0                                               | 99              |

|----------|----------------|---------|-------------------------------------------------------|-----------------|

|          |                | 4.6.4   | Validation in simulation and identified issues        | 03              |

|          |                |         | *                                                     | 03              |

|          |                |         | 1 0                                                   | 04              |

|          |                |         | 0 00 1                                                | 05              |

|          |                |         | Node discharge dependency                             | 06              |

|          |                | 4.6.5   | Results                                               | 06              |

|          |                |         | Weight programming                                    | 06              |

|          |                |         | Operating point                                       | 07              |

|          |                |         | Complete interactive demonstrator                     | 08              |

|          | 4.7            | Conclu  | i <mark>sion</mark>                                   | 08              |

|          |                | 4.7.1   | FeFET-based logic                                     | 08              |

|          |                | 4.7.2   | Image filter                                          | 10              |

|          |                | 4.7.3   |                                                       | 10              |

|          |                |         |                                                       |                 |

| <b>5</b> | $\mathbf{Des}$ | ign spa | ace exploration and optimization 11                   | 13              |

|          | 5.1            | Introdu | uction to design space exploration                    | 14              |

|          |                | 5.1.1   | Parameter space and performance space, Pareto optimal | 14              |

|          |                |         | Parameter and performance space                       | 14              |

|          |                |         |                                                       | 15              |

|          |                |         |                                                       | 15              |

|          |                | 5.1.2   | Tool-assisted exploration                             | 15              |

|          |                |         | Process                                               | 16              |

|          |                | 5.1.3   | System-level benchmarking                             | 17              |

|          | 5.2            | Design  |                                                       | 17              |

|          |                | 5.2.1   |                                                       | 17              |

|          |                | 5.2.2   |                                                       | 18              |

|          | 5.3            | Design  |                                                       | 19              |

|          |                | 5.3.1   |                                                       | 19              |

|          |                |         |                                                       | 19              |

|          |                |         |                                                       | 19              |

|          |                |         |                                                       | 20              |

|          |                |         |                                                       | 23              |

|          |                |         |                                                       | 23              |

|          |                | 5.3.2   |                                                       | 25              |

|          |                | 0.0.2   | • (                                                   | $\frac{25}{25}$ |

|          |                |         |                                                       | $\frac{25}{27}$ |

|          |                |         |                                                       | 27<br>27        |

|          | 5.4            | System  |                                                       | 29              |

|          | 0.1            | 5.4.1   | · · · · · · · · · · · · · · · · · · ·                 | $\frac{25}{29}$ |

|          |                | 0.4.1   |                                                       | $\frac{25}{29}$ |

|          |                |         | · ·                                                   | $\frac{25}{29}$ |

|          |                |         |                                                       | $\frac{29}{29}$ |

|          |                | 5.4.2   |                                                       | $\frac{29}{29}$ |

|          |                | 0.4.2   |                                                       | 29<br>29        |

|          |                |         |                                                       | 29<br>29        |

|          |                |         |                                                       | 29<br>30        |

|          |                | 5.4.3   |                                                       |                 |

|          |                | 0.4.5   | <u>.</u>                                              | 30<br>31        |

|          |                |         |                                                       |                 |

|          |                |         | • •                                                   | 32              |

|          |                |         |                                                       | 32              |

|          |                |         |                                                       | 32              |

|          |                | F 4 4   |                                                       | 32              |

|          |                | 5.4.4   | •                                                     | 33              |

|          |                |         | ·                                                     | 33              |

|          |                |         | -                                                     | 33              |

|          |                |         | •                                                     | 33              |

|          |                |         | Model card structure                                  | 34              |

|              |        | 5.4.5 Example case: Adder                          | 134 |

|--------------|--------|----------------------------------------------------|-----|

|              | 5.5    | System-level exploration results                   | 135 |

|              |        | v v v v v v v v v v v v v v v v v v v              | 136 |

|              |        | •                                                  | 137 |

|              |        | *                                                  | 138 |

|              | 5.6    |                                                    | 139 |

|              |        |                                                    | 139 |

|              |        | · · · · · · · · · · · · · · · · · · ·              | 139 |

|              |        | 6 F 111                                            | 140 |

|              |        |                                                    | 140 |

|              |        | · · · · · · · · · · · · · · · · · · ·              | 140 |

|              |        | Design-Technology Co-Optimization                  | 140 |

| 6            | Con    | nclusion                                           | 143 |

|              | 6.1    | Back-End of Line ferroelectric technology          | 143 |

|              | 6.2    |                                                    | 144 |

|              |        |                                                    | 144 |

|              | 6.3    |                                                    | 144 |

|              |        | 6.3.1 Modeling issues                              | 144 |

|              | 6.4    | System-level performance evaluation                | 145 |

|              | 6.5    | Short-term perspectives                            | 145 |

|              |        |                                                    | 145 |

|              |        | 6.5.2 Future simulations                           | 145 |

|              | 6.6    | Future considerations for ferroelectric technology | 146 |

|              |        | 6.6.1 Space efficiency                             | 146 |

|              |        | 6.6.2 Control signals                              | 146 |

| Bi           | ibliog | graphy                                             | 147 |

| $\mathbf{G}$ | lossa  | ry                                                 | 159 |

| A            | crony  | yms 1                                              | 163 |

| A            | Cod    | le listings                                        | 165 |

|              |        |                                                    | 181 |

|              |        |                                                    | 183 |

| •            | Aut    | HUICHAI VADICO                                     |     |

# List of Figures

| 1.1                 | Von Neumann Architecture diagram                                                   | 20              |

|---------------------|------------------------------------------------------------------------------------|-----------------|

| 2.1                 | Effect of domain orientation on external and coercive field mismatch               | 25              |

| 2.2                 | Ferroelectricity illustration with spring-charge equivalent system                 | 25              |

| 2.3                 | Experimental domain orientation measurement in Si-Doped HfO <sub>2</sub>           | 26              |

| 2.4                 | Reading Pr and $V_C$ on a curve                                                    | 28              |

| 2.5                 | Example P-V curves                                                                 | 28              |

| 2.6                 | Electrical polarization and relationship with ferroelectricity                     | 29              |

| $\frac{2.0}{2.7}$   | Band diagrams with screening length                                                | $\frac{23}{31}$ |

| 2.8                 | PUND measurement illustration                                                      | 32              |

| 2.9                 | Pure ferroelectric <i>P-V</i> response extracted through PUND stimulation          | 34              |

|                     | Plots of Gibbs free energy and its derivative for the Landau model                 | 35              |

|                     | Fitting a Landau polynomial to experimental data                                   | 38              |

|                     | Example ferroelectric hysteresis cycle                                             | 39              |

| $\frac{2.12}{9.19}$ | Preisach model – hysterons and plane                                               | 39              |

|                     | $(V_c^+, V_c^-)$ 2D Gaussian distribution                                          | 41              |

|                     |                                                                                    | 41              |

|                     | Internal loops and turning points                                                  |                 |

|                     | Example of 2D $V_c^+/V_c^-$ Gaussian distribution extraction                       | 42              |

|                     | Handling arbitrary $V_c^+/V_c^-$ distributions                                     | 42              |

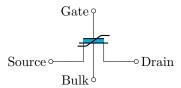

|                     | FeFET symbol and gate stack                                                        | 45              |

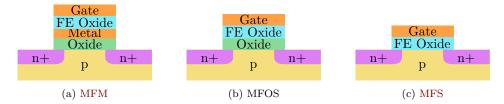

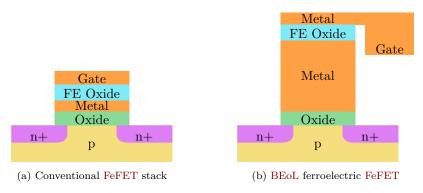

|                     | FeFET gate stacks                                                                  | 47              |

| 2.20                | System-level performance evaluation landscape                                      | 51              |

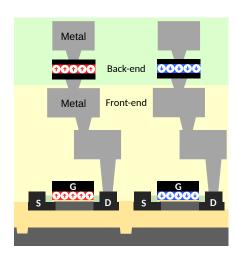

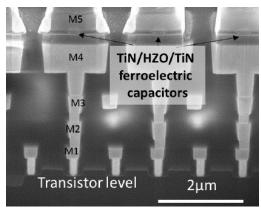

| 3.1                 | Illustration of front-end and back-end ferroelectric technologies                  | 54              |

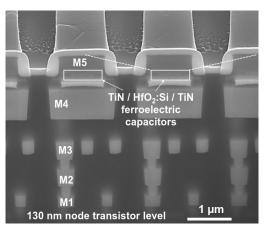

| 3.2                 | Electron microscope image of the MAD200 layers                                     | 55              |

| 3.3                 | Cutaway comparison of a FeFET and PsFeFET stack                                    | 59              |

| 3.4                 | Comparison cutaway of FEoL and BEoL ferroelectric technologies                     | 60              |

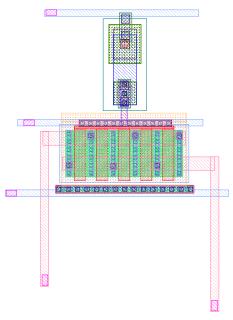

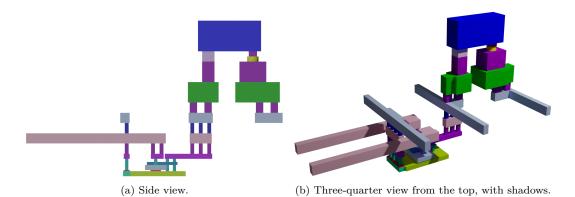

| 3.5                 | 3D PsFeFET layout                                                                  | 63              |

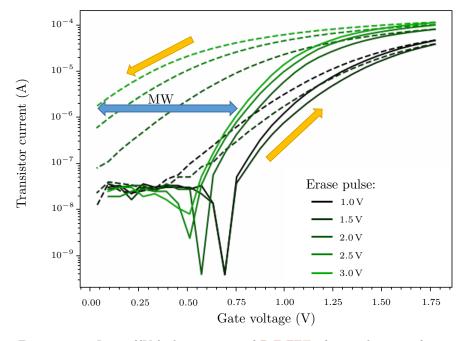

| 3.6                 | $I_D = f(V_G)$ characteristic of a PsFeFET                                         | 64              |

| 3.7                 | Programming voltage and 2T1C memory window                                         | 75              |

| 3.8                 | Pulse width effect on 2T1C memory window                                           | 76              |

| <b>9.</b> 0         | Tuise with effect on 2110 memory window                                            | 70              |

| 4.1                 | $V_{th}$ shifting illustration                                                     | 81              |

| 4.2                 | Black & Das cell behavior                                                          | 92              |

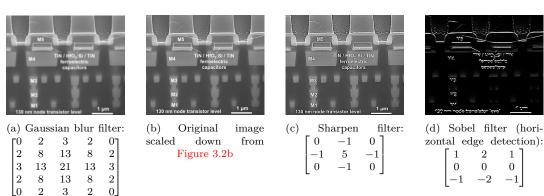

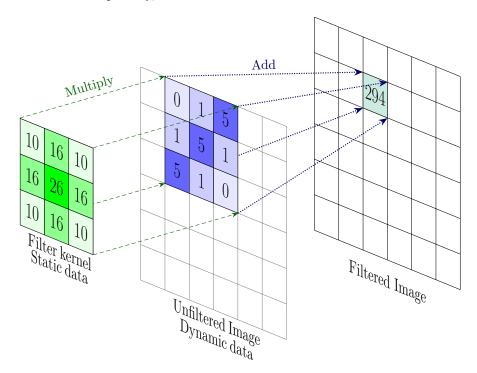

| 4.3                 | Filter kernel examples                                                             | 93              |

| 4.4                 | Illustration of a convolutional image filter                                       | 94              |

| 4.5                 | High-level diagram of the proposed image filter                                    | 95              |

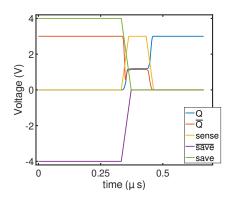

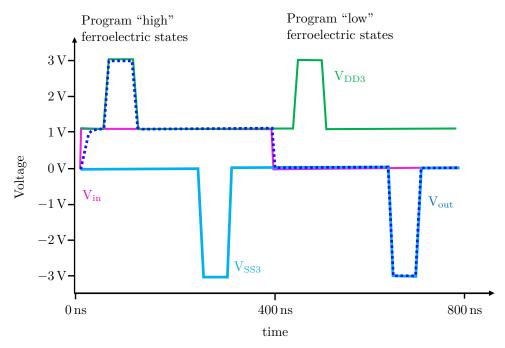

| 4.6                 | Input and output signals of the programming voltage multiplexer                    | 103             |

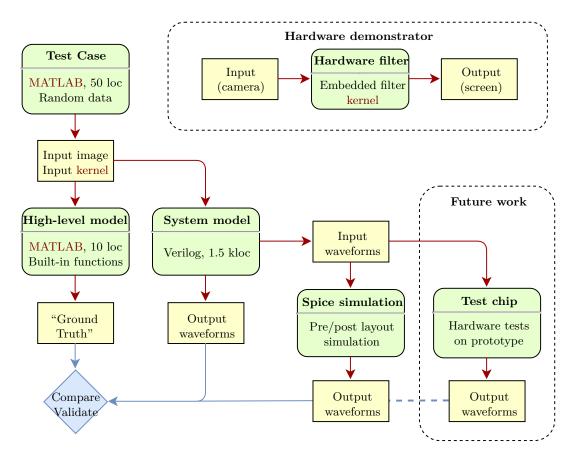

| 4.7                 | Verification flow employed to validate the image filter design                     | 104             |

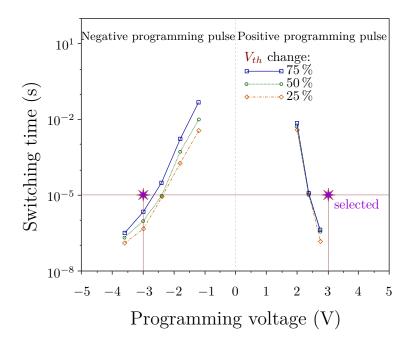

| 4.8                 | Measurements of the $V_{th}$ shift depending on pulse duration and voltage $\dots$ | 107             |

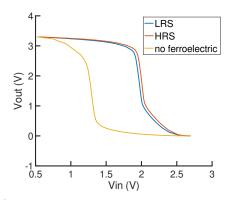

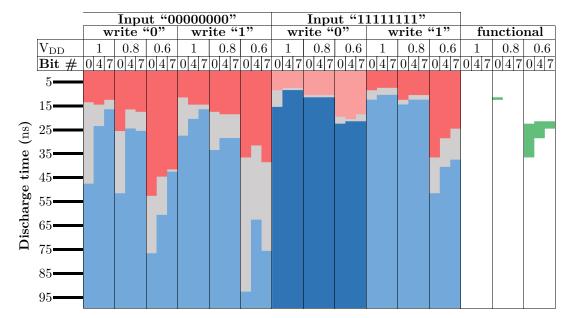

| 4.9                 | Image filter dynamic characterization results and operating point                  | 109             |

|                     |                                                                                    | 44.             |

| 5.1                 | Illustration of complexity increase due to combinatorial explosion                 | 114             |

| 5.2                 | Parameter space and performance space; Pareto set and front                        | 115             |

| 5.3                 | Experimental and Simulation-based approaches to performance measurement            | 116             |

| 5.4                 | Automated Design-Space Exploration approach                                        | 117             |

| 5.5                 | Pareto front and set generation flow                                               | 117             |

| 5.6                 | Cadence IPC architecture                                                           | 118             |

| 5.7                 | Annotated 1T1C test waveforms                                                      | 121             |

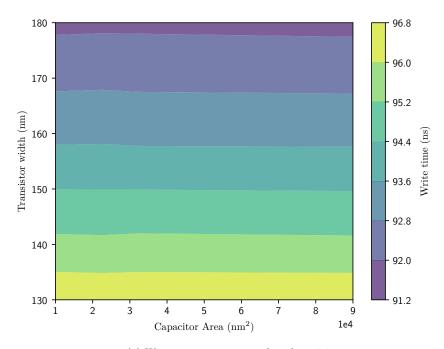

| 5.8  | DSE results for 1T1C exploration: time, memory window vs transistor geometry. | 124 |

|------|-------------------------------------------------------------------------------|-----|

| 5.9  | DSE results for 1T1C exploration: time and energy vs capacitor area           | 126 |

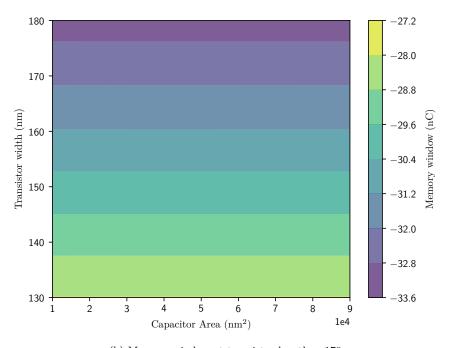

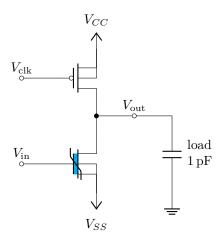

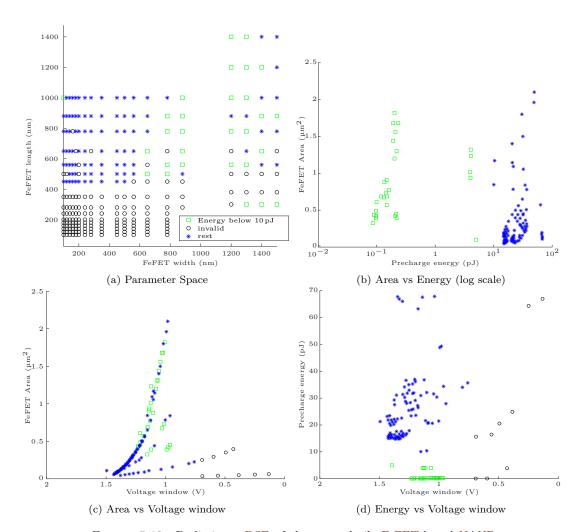

| 5.10 | Preliminary DSE of the non-volatile FeFET-based NAND gate                     | 128 |

| 5.11 | Illustration of coarse- and fine-grained LiM                                  | 130 |

| 5.12 | Illustration of a Logic-in-Memory-based accelerator on the system bus         | 130 |

| 5.13 | Benchmarking platform internal structure diagram                              | 131 |

| 5.14 | Simulation platform architecture: model cards and operation manager           | 133 |

| 5.15 | Illustration of the common operation interface                                | 133 |

| 5.16 | Execution diagram of the operation module                                     | 134 |

| 5.17 | Addition operation performed by the example accelerator                       | 135 |

| 5.18 | Benchmarking platform inputs and outputs                                      | 135 |

| 5.19 | Benchmarking platform results for normally-off computing                      | 137 |

| 5.20 | Exploration of LiM trade-off: interpolator vs LUT multiplier                  | 138 |

| 5.21 | Energy use of WB and NWB strategies for matrix multiplication                 | 139 |

| 5.22 | DTCO pipeline combining system-level performance and device-level parameters  | 141 |

# List of Circuits

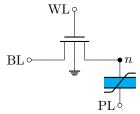

| 3.1  | 1T1C bitcell                                                      | ó |

|------|-------------------------------------------------------------------|---|

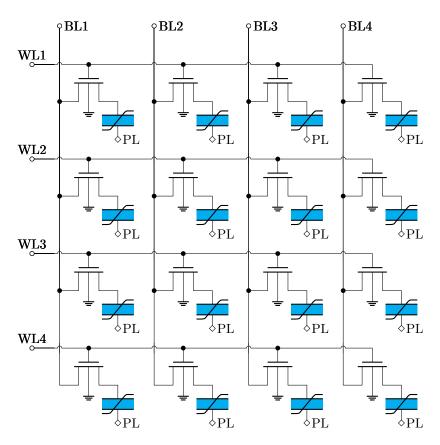

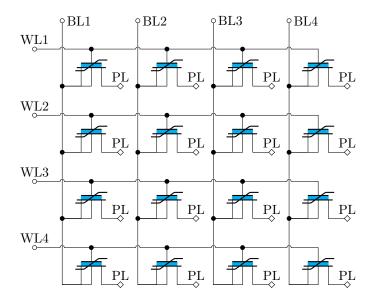

| 3.2  | $4 \times 4$ 1T1C array                                           | 3 |

| 3.3  | PsFeFET and FeFET electrical circuits                             | ) |

| 3.4  | PsFeFET and equivalent schematic 61                               | 1 |

| 3.5  | Equivalent PsFeFET floating capacitors circuit 61                 | 1 |

| 3.6  | PsFeFET layout                                                    | 3 |

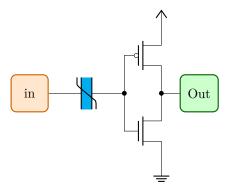

| 3.7  | PsFeFET-based CMOS with shared FeCap 65                           | 5 |

| 3.8  | Destructive-read TCAM schematic                                   | 3 |

| 3.9  | Destructive-read TCAM layout                                      | 3 |

| 3.10 | 2T1C bitcell schematic                                            | ) |

| 3.11 | 2TnC schematic                                                    | ) |

| 3.12 | 2T1C layout                                                       | 2 |

| 3.13 | 2T3C structure as designed                                        | 3 |

|      |                                                                   |   |

| 4.1  | FeFET Symbol                                                      |   |

| 4.2  | 1T-FeFET bitcell                                                  |   |

| 4.3  | $4 \times 4$ 1T-FeFET array                                       |   |

| 4.4  | Transresistance circuit with complementary FeFET                  |   |

| 4.5  | FeFET circuit with resistor-based transresistance                 |   |

| 4.6  | Transresistance with dynamic logic architecture                   |   |

| 4.7  | Hybrid CMOS and dynamic logic architecture                        |   |

| 4.8  | FeFET-based pass transistor and associated truth table 89         |   |

| 4.9  | NAND FeFET-based logic gate                                       |   |

|      | AND FeFET-based logic gate                                        |   |

|      | XOR FeFET-based logic gate                                        |   |

|      | Black & Das FeFET-enhanced SRAM                                   |   |

|      | Image filter architecture diagram                                 |   |

|      | Shift register internal diagram                                   |   |

|      | Final FeFET-based Full-Adder multiplier                           |   |

|      | Ripple-Carry Adder based on full adders                           |   |

|      | Image filter multiplier pipeline stages                           |   |

| 4.18 | Voltage multiplexer used for programming the multiplier FeFET 102 | 2 |

| 5.1  | 1T1C bitcell schematic and test power supplies                    | ) |

| 5.2  | Dynamic NV-NAND2 circuit for DSE                                  |   |

| 0.2  | Dynamic IV IVIII De Circuit for Dob                               | 1 |

| B.1  | First version of the full adder for the multiplier circuit        | l |

| B.2  | Second iteration of the full adder for the multiplier circuit     | 2 |

| B.3  | •                                                                 | ) |

# Listings

| 2.1  | Verilog-A Minimal ferroelectric model                                             | 43  |

|------|-----------------------------------------------------------------------------------|-----|

| 5.1  | Memory model card template                                                        | 134 |

| 5.2  |                                                                                   | 134 |

| 5.3  | Execution trace for performing an addition                                        | 135 |

| A.1  | SKILL® Metric extraction from waveforms for 1T1C bitcell                          | 165 |

| A.2  | SKILL Metric extraction from waveforms for FeFET-based NAND gate                  | 167 |

| A.3  | 1T1C Design space exploration python script                                       | 169 |

| A.4  | FeFET-based non volatile NAND design space exploration script                     | 170 |

| A.5  | Verilog-A Data Serializer                                                         | 171 |

| A.6  | Verilog-A Data Serializer with enable signal                                      | 172 |

| A.7  | GNU Octave code for fitting Landau coefficient to experimental curves             | 173 |

| A.8  | GNU Octave code for orthogonal projection (dependency)                            | 176 |

| A.9  | GNU Octave code for polynomial fit with constraints on coefficients (dependency)  | 176 |

| A.10 | GNU Octave code for image filtering with convolutionnal kernels                   | 177 |

| A.11 | Verilog description of falling edge sensitive shift register with alternate input | 177 |

| A.12 | Verilog description of shift register with alternate input and adjusted sampling  | 178 |

| A.13 | Synthesized Verilog description of 1-bit shift register                           | 178 |

| A.14 | Kernel programming FeFET-based image filter Verilog testbench                     | 179 |

## Chapter 1

## Introduction

| Contents |                                                             |

|----------|-------------------------------------------------------------|

| 1.1      | About this document                                         |

|          | 1.1.1 License                                               |

|          | 1.1.2 Internal links and color code                         |

|          | 1.1.3 Document source, errata and supplementary material 16 |

|          | 1.1.4 Aim of this document                                  |

| 1.2      | Context                                                     |

|          | 1.2.1 Internet of Things and edge computing                 |

|          | 1.2.2 The demise of Dennard scaling and Moore's law         |

|          | 1.2.3 Von Neumann Architecture                              |

|          | 1.2.4 Von Neumann Bottleneck                                |

|          | 1.2.5 Ferroelectric HfZrO <sub>2</sub>                      |

|          | 1.2.6 Conclusion                                            |

| 1.3      | 3εFERRO European project                                    |

|          | 1.3.1 Project partners                                      |

|          | 1.3.2 Project Goals                                         |

#### 1.1 About this document

#### 1.1.1 License

This work is licensed under a Creative Commons "Attribution 4.0 International" license.

In simple terms, this means you are free to use both the text (including code) and images of this document, as well as remixing and adapting it, as long as you properly attribute it. For more details, please consult the above link, or the Creative Commons website at <a href="https://creativecommons.org/licenses/by/4.0/deed.en">https://creativecommons.org/licenses/by/4.0/deed.en</a> The license does not apply to figures provided by external sources, as noted in the captions.

#### 1.1.2 Internal links and color code

This document contains both internal and external links that can be followed by a compatible reader. These links are color-coded as follows:

- 1. Internal links to sections, figures, code listings and various parts of the document

- 2. Internal links to the Bibliography section

- 3. Internal links to the Glossary and list of Acronyms

- 4. External links to websites

#### 1.1.3 Document source, errata and supplementary material

An up-to-date revision of this document, as well as its LATEX source code and supplementary material (code listings as well as additional data) are available at https://thesis.mayeul.net <sup>1</sup>.

#### 1.1.4 Aim of this document

This document aims to both summarize the work accomplished and the results obtained over the course of this PhD; as well as serving as a self-contained introductory document to ferroelectric circuits design.

#### 1.2 Context

For decades, the microelectronics industry has seen exceptional growth in both size and capabilities. Constant technological improvements were achieved through miniaturization, bringing both continuous performance and efficiency gains. The industry is now structured around these expected gains, but while there initially was "plenty of room at the bottom" (to cite Feynman) for miniaturization, this is not the case anymore, and continuing to increase the density of integrated circuits will entail geometry changes, as Fin FETs (FinFETs) are now common in most advanced nodes, and vertical nanowires [Poi22] are envisioned.

Another possible avenue for performance and energy efficiency increases does not involve increasing density, but rather enable new functionality at a similar miniaturization level. This is the case for changes to devices such as Fully Depleted Silicon on Insulator (FDSOI) transistors and Ferroelectric Field-Effect Transistors, but also for changes to computing architectures, that can provide tangible performance gains.

Besides economic considerations (new technology driving sales by obsoleting previous generations of devices), energy efficiency gains are important to offset the growing ecological and energetic footprint of electronics devices. These gains are offset to an extent by a rebounding effect, as cheaper, more powerful and more energy efficient devices enable new use-cases. This however brings an increase in capabilities that is hardly quantifiable, and makes technology affordable.

In this introduction, the existing trends in microelectronics are summarized, highlighting why the previous approach to efficiency gains is not sufficient anymore. New use-cases such as the Internet of Things (IoT) and edge computing are described, as well as one specific emerging technology, based on ferroelectric  $HfZrO_2$ , and the associated  $3\varepsilon FERRO$  European project this work is part of.

#### 1.2.1 Internet of Things and edge computing

#### Internet of Things

The IoT comprises a multitude of devices and device classes. Those are usually sensors, that measure physical quantities such as temperature, humidity or atmospheric pressure, or more specific values such as energy usage, the number of cars in a parking lot, movement sensors as part of an alarm system, etc. More complex devices can also be considered IoT, such as modern, Internet-connected cars, or "smart" devices that are getting more common in homes, like thermostats, network-enabled kettles, lights, curtains, cat litters... These devices sometimes include actuators as well as sensors, some of which can be safety-critical, such as a barrier controlling access to a highway emergency exit ramp.

IoT is a fast-growing market, as data collection, and access to supplementary data from the Internet enables much more complex behaviors. For instance, the use of temperature and soil humidity sensors could help monitor crops; and connecting an irrigation system to weather forecasts could save water. However, as opposed to the cloud, which is made up of expensive, powerful and servers in electrical grid-connected datacenters, IoT is usually cheap, expendable, with energy and connectivity constrains. Cost and power-efficiency means

$<sup>^{1}</sup> mirrors \ available \ at \ https://these.mayeul.net, https://mayeulc.gitlab.io/thesis, https://thesis.mayeul.cantan.eu \ and \ https://mayeulc.github.io/thesis$

1.2. Context 17

that IoT devices generally have very limited amounts of memory and computing power. Indeed, be it a moisture sensor in the middle of a field, a pressure sensor on the rim of a car wheel, or an open/closed sensor at the top of a window, supplying electrical power to these devices is often challenging, leading to a large number of battery-operated devices, sometimes supplemented by energy harvesting mechanisms: solar panels, triboelectricity or vibrational energy harvesters, peltier or thermoelectric modules to harvest waste heat, etc. This also means these devices often rely on a wireless connection to transmit data, which requires a relatively important amount of power: according to the datasheet[Esp22], a very common ESP8266EX typically consumes around 50 mW with its radio modem turned off, while transmitting data at 15 dBm uses an order of magnitude more power. With its CPU turned off, that device only consumes only 0.5 mW to 20 mW.

#### Edge computing

IoT makes extensive use of the cloud as a data source and sink. However, as detailed above, transmitting data has a non-negligible energy cost for battery-backed devices. This also becomes a bandwidth issue once data reaches the servers: Internet transit costs can be quite substantial, and processing cost rises with the amount of data.

Edge computing aims to relocate some of the processing tasks outside of the cloud, to its periphery or *edge*. This concerns data processing that is too intensive to perform on the IoT devices themselves due to resource constraints, but where applying some amount of pre-processing can reduce latency and bandwidth sent to the cloud.

In practice, processing data as close as possible to the source usually results in efficiency gains. For instance, in a video surveillance system, a wireless camera (IoT device) can avoid transmitting data when no movement is detected, and compress the video feed before sending it to save energy during transmission. That feed would then be sent to a more powerful intermediate *edge device* for further processing. This could include an image recognition task, identifying a fox in a chicken farm, or an armed person in a crowd. That edge device therefore performs relatively intensive processing tasks to pre-filter data before sending it to remote servers for further processing. In the above example, this could be archiving the video, or transmitting it to another device.

Another example is voice assistant can also perform basic voice recognition locally, to answer commands faster, but also to send text instead of voice to the cloud; this also has availability and privacy benefits.

#### 1.2.2 The demise of Dennard scaling and Moore's law

#### Moore's Law

Moore's law was formulated in 1965[Moo65] by Gordon Moore (Intel co-founder, 1929–2023), stating that the number of features (i.e. transistors) on an integrated circuit doubled every two years for the best-priced chips (smallest cost per feature). This is usually roughly summarized as transistor density doubling every two years. That observation held for much longer than initially anticipated, although that is partly due to the industry using it as a roadmap for development, including factory investments, R&D spending, and product planning.

#### Dennard scaling

After the industry's transition to Metal-Oxide-Semiconductor Field-Effect Transistor (MOS-FET) transistors, Dennard scaling was identified in 1974[Den+74] as a practical way to continue increasing the transistor density, by reducing transistor dimensions as specified in Table 1.1. The values are constructed by scaling transistors down while keeping the electrical field constant.

This scaling method led to a sustained density improvements over the following years, the period from 1980 to 1995 being nicknamed the era of "happy scaling". Thanks to improved manufacturing methods, devices and circuits could be scaled down at a regular pace. The reduced component and interconnection size lowered capacitance, increasing both maximum operating frequency, and energy efficiency by reducing switching losses.

| Scaling Factor |

|----------------|

| $1/\kappa$     |

| $\kappa$       |

| $1/\kappa$     |

| $1/\kappa$     |

| $1/\kappa$     |

| $1/\kappa^2$   |

| 1              |

|                |

TABLE 1.1: Dennard scaling parameters and results on performance, from [Den+74]. Note the constant power density.

To remain in line with Moore's law,  $\kappa$  was chosen to halve transistor surface area  $A \approx L \cdot W$  each generation:  $1/\kappa^2 = 1/2 \implies \kappa = \sqrt{2} \approx 1.4$ [Boh07], roughly every two years.

#### "Happy scaling" consequences

Constant performance gains had a rippling effect across the industry: it was often possible to reuse previous chip designs, scale them down, manufacture them with the improved process, and obtain performance gains as a result. Moreover, algorithms designed for general-purpose processors could reap these benefits as well, provided backwards compatibility was maintained across chip generations. Maintaining backwards compatibility with older hardware and software generations proved beneficial for iterative improvements, and lasting investments.

As a result, general purpose processor architectures, and associated algorithms, toolchains and compilers have leapfrogged specific-purpose hardware: in some cases, ASICs and custom processor architectures may have offered performance and efficiency benefits over Central Processing Unit (CPU)-based implementations, but the long design process combined with steady performance increases means that CPU performance could catch up with the application-specific design before it was available.

The current hardware and software ecosystem must be observed through that lens, and this work reflects the recent interest renewal in alternative approaches.

#### End of Dennard scaling

Dennard scaling is not sustainable indefinitely, as there are engineering, manufacturing and physical limits to doing so: voltages cannot drop below a certain level, as this would degrade the signal-to-subthreshold current noise ratio. Doping concentrations becomes hard to increase as size shrinks, leading to issues such as uneven atomic distribution and direct band-to-band tunneling across PN (transistor source and drain) junctions[Boh07]. Dimensions also have fundamental limits, as tunneling current becomes non-negligible below a certain size (depending on the voltage and other factors, around 20 nm).

As feature size shrunk below  $65\,\mathrm{nm}$ , leakage currents became more important, starting with transistor gate insulators, which were  $1.2\,\mathrm{nm}$ , or about five  $\mathrm{SiO}_2$  atomic layers thick by  $2005[\mathrm{Boh}07]$ . This led to the introduction of "high-k" dielectrics in order to maintain the same electrical field in the transistor channel despite using thicker gate oxides, reducing leakage current, but also breaking with Dennard scaling. Beyond this point, constant-field scaling encountered more issues which required rethinking the approach to device scaling.

The end of Dennard scaling had a notable effect on integrated circuits power dissipation: as voltages could not be lowered much further, and leakage currents were increasing, the power density could not remain constant anymore. This resulted in substantial power usage increases for modern chips and processor circuits. Power efficiency can still be improved thanks to increased performance, while leakage current can be mitigated by disabling the power supply of unused chip areas, a so-called "dark silicon" approach.

#### End of Moore's Law

While transistors were able to continue scaling down post-Dennard scaling for a few years, the end of planar MOSFET technology scaling was in sight. With no clear scaling roadmap,

1.2. Context 19

investments required to follow the roadmap plotted by Moore continued to grow rapidly, further consolidating the semiconductor industry.

More recently, density increases fell short of Moore's predictions, and have been achieved through more important changes to the Field Effect Transistor (FET) architecture, with the generalization of FinFET, and the development of Gate-All-Around FET (GAAFET) and vertical nanowire FETs. These designs achieve transistor density gains largely by exploiting the vertical dimension, without substantially reducing feature size.

Another avenue for continuing to increase the number of features per chip is to increase chip size, with recent developments being made in wafer-scale chips. However, this is unlikely to completely offset the rising costs of the latest generation semiconductor nodes, that reflect the important investments necessary to continue increasing transistor density.

Future performance improvements are expected to come from both density increase (albeit at a slower pace), but also from new system architectures and devices, possibly non-electrical (photonics, molecular storage). A variety of labels have been used to describe these approaches, including "more Moore" and "more than Moore".

Power efficiency is possibly an even greater challenge than continued density improvements, without constant power-density Dennard scaling. Thermal issues are worsened by the move away from planar transistors, which were able to maximize contact area with the silicon die for thermal dissipation.

Reflecting this change of direction, the industry reinvents itself, and is investigating multiple emerging technologies, including a re-evaluation of some that fell out of favor during the "happy scaling" era. The reduced pace of performance improvement for conventional transistor may also finally allow alternatives to catch up performance-wise. This work presents one such thread of investigation into ferroelectric materials for bringing new functionalities to existing semiconductor technologies.

The International Technology Roadmap for Semiconductors (ITRS), coordinating different companies toward the development of next-generation silicon devices also illustrated this trend in 2016, becoming the International Roadmap for Devices and Systems (IRDS). Their reports offer an overview of the technologies under development and their potential applications[IRDS22].

#### 1.2.3 Von Neumann Architecture

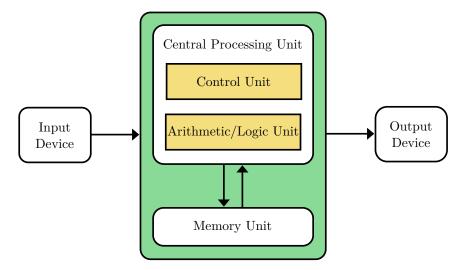

Computers today are overwhelmingly designed around the concept of stored programs: by storing programs in memory, these can be easily loaded and modified, as well as copied and transferred. This makes computers much more versatile by not requiring to physically alter them in order to perform a new function [Knu70], unlike early architectures.

One of the most used computer architectures following this paradigm is the Von Neumann architecture pictured in Figure 1.1, and its derivatives[Paw22]. Named after John von Neumann, it reads both instructions and data from the same memory, through a memory bus. As a generalization of this architecture, multiple peripherals, including Input/Output (I/O) devices, can be present on the memory bus (or system bus) at known addresses, and communicate using the same interface made of a data and address bus, with read and write operations. This generalization helped make computer architectures very modular, only having to rely on a common abstraction for most use-cases. "Peripherals" such as additional I/O adapters, coprocessors or specialized devices can communicate with the CPU and program running on it by interfacing with this unique memory bus.

#### 1.2.4 Von Neumann Bottleneck

Due to the importance of the system bus in Von Neumann-Derived architectures, it occupies a central place in processor designs, constraining system performance with its physical footprint, transfer speed and energy usage. As circuit speed increase, the amount of data that needs to be transferred not to starve off the processor rises, further straining memory and system buses.

Modern processors make use of multiple levels of hierarchical caches to reduce external memory accesses in order to reduce latency and increase availability of the memory

FIGURE 1.1: Von Neumann Architecture diagram, adapted CC-BY-SA work from [Kap13].

buses, while reducing power consumption. However, caching is insufficient, as its effectiveness is highly dependent on the algorithm. Moreover, Static Random Access Memory (SRAM) density increase seems to slow down[Sch22] despite cache size continuously growing, attaining multiple gigabytes on commercial offerings through technologies such as 3D stacking[Wuu+22]. The number memory controllers and system buses is also increasing, which makes signal routing more complex, and requires a higher amount of I/O pads[Bec+18].

Another major concern is the increasing fraction of the total available power budget being used to transmit data. Power requirements, measured in Jbit<sup>-1</sup>, increases linearly with bandwidth. This makes data transmission one of the largest sources of power dissipation inside microprocessors[BI13], despite careful management of the energy budget[Bec+18].

Multiple other ways to alleviate this bottleneck are being explored, including non-electrical data transmission using radiofrequency [Cha+08] or optical interconnects [Liu+14], as well as alternative architectures merging processing and memory to reduce the need for data transmission. This thesis focuses on the latter approach.

#### 1.2.5 Ferroelectric HfZrO<sub>2</sub>

Hafnium and Zirconium oxide have been employed for years [WSW00] as high permittivity (high-k) dielectrics in semiconductor applications, especially below 45 nm, as deployed by Intel in 2007 with its "Penryn" processor line using Hafnium-based high-k gate oxides.

In 2006, during the development of dielectric materials for Dynamic Random Access Memory (DRAM) capacitor applications at Infineon/Qimonda (Dresden/Germany), a variety of different doped HfO<sub>2</sub> and ZrO<sub>2</sub> thin films were analyzed, revealing nonstandard switching behavior in silicon-doped HfO<sub>2</sub> at some concentrations[SHF19]. Upon further analysis, it was revealed that under some doping and annealing conditions, the material could crystallize into a non-centrosymmetric structure, compatible with ferroelectricity. This led to the first series of publications in 2011[Bös+11a; Bös+11b; Mül+11], ushering us into a revolutionary era for scaled down ferroelectric devices.

A variety of dopants may be employed to allow hafnium oxides to crystallize into a ferroelectric phase, although Zirconium is generally favored thanks to its low annealing temperature of 500 °C[Bou20, p. 144].

Indeed, ferroelectric Hafnium presents multiple advantageous characteristics compared to previous ferroelectric materials:

CMOS compatibility: this is the most interesting property, as hafnium oxide was already

widely in use within industrial CMOS processes as a gate oxide material.

- Low coercive electric field: from  $0.5\,\mathrm{MV\,cm^{-1}}$  to  $2.5\,\mathrm{MV\,cm^{-1}}$  [Bou20, p. 145], typically at  $1.2\,\mathrm{MV\,cm^{-1}}$ , this allows coercive voltages around  $1.2\,\mathrm{V}$  for a typical 10 nm oxide thickness, which are compatible with CMOS logic levels.

- Low annealing temperature: at 500 °C, HfZrO<sub>2</sub> can be deposited above CMOS devices without damaging them.

- Temperature-stable: Curie temperature can easily surpass 200 °C[Bou20, p. 143], depending on doping concentration and transistor size. This is interesting for Non-Volatile Memory applications.

#### 1.2.6 Conclusion

Since the end of Dennard's scaling circa 2005, power density of integrated circuits has grown, leading to a search for more energy-efficient circuit designs and architectures. This is compounded by the end of Moore's "law", where conventional "planar" transistor architectures have reached physical scaling limits. New avenues are being explored for increasing density, with excursions in the 3<sup>rd</sup> dimension for circuit and transistor designs. However, these approaches also increase the power density, leading to power dissipation issues. At the same time, increasing performance continues to highlight bottlenecks of the Von Neumann architectures and derivatives.

New applications with extremely high performance or power efficiency requirements have also surfaced: genetics, big data applications including machine learning, as well as IoT, smart and embedded sensor networks, etc. These are increasingly using application-specific architectures and devices instead of general-purpose CPUs, now undoing a trend that started in the 1980s. High-performance needs are now served by Graphics Processing Units (GPUs) and Tensor Processing Units (TPUs), as well as other purpose-built ASIC. High energy-efficiency needs are also served by ASICs and FPGAs, with FDSOI transistors.

As a result, interest has been renewed in alternatives to both Von Neumann architectures and CMOS-based circuits.

#### 1.3 $3\varepsilon$ FERRO European project

The work presented in this document is part of a wider European project:  $3\varepsilon FERRO$  (standing for Energy Efficient Embedded Non-volatile Memory Logic based on Ferroelectric  $Hf(Zr)O_2$ ). As part its dissemination activities, the project hosts a website at https://www.3eferro.eu, and commissioned an introductory video available at https://youtu.be/M8tL-nN7G-A, which is effective at conveying an entry-level overview of the goals and context.

#### 1.3.1 Project partners

The project counts eight participants, with various areas of expertise. As such, our team had more opportunity to interact with some partners than others. Our closest collaborators figure at the top of the following list of partners:

- 1. INL, as part of ECL, Lyon, France

- 2. NaMLab, Dresden, Germany

- 3. STMicroelectronics, Grenoble, France

- 4. CEA-LETI, Grenoble, France

- 5. EPFL, Lausanne, Switzerland

- 6. Demokritos, Athens, Greece

- 7. NIMP, Bucharest, Romania

- 8. FZJ, Jülich, Germany

#### 1.3.2 Project Goals

This project has a wide scope, reflected in the aforementioned partners. Its main objective is to develop technologies related to the integration of ferroelectric  $HfZrO_2$  with more traditional microelectronics processes.

The approach can be seen as a bottom-up one, starting with material science and characterization of deposited oxides, as well as the optimization of manufacturing process and material properties; then with device and circuit design, characterization and modeling, up to technological demonstrators and architecture performance predictions.

#### Achievements

This project advanced the state of the art for ferroelectric HfZrO<sub>2</sub> integration.

Deposition methods<sup>2</sup> were improved[Fra+19b] to optimize the performance of the ferroelectric layer, including the optimization of annealing cycles, temperature and pressure[Bou+19], material and substrate composition[Zac+22]. A lot of effort was spent to improve reliability and yield, to obtain uniform characteristics across devices and wafers, with advanced characterization methods including electrical and microscopic characterization, piezoresponse force microscopy, as well as hard and soft X-ray photoelectron spectroscopy, leading to better models. Device properties were investigated, including Ferroelectric Capacitors (FeCaps), Ferroelectric Field-Effect Transistors (FeFETs) and negative capacitance[Gas+19] for use in Negative-Capacitance Field-Effect Transistors (NCFETs). Several circuits and demonstrators were also realized, including 16 kbit memory arrays[Fra+19a; Fra+21].

The project demonstrated the viability of doped Hafnia-based memory devices, and its competitiveness with flash memories in terms of speed, endurance, retention, energy consumption, density, and ease of integration[Gre+20; Oku+21; Alc+22].

#### Contributions

Our contributions, as outlined in this document, mainly focus on the circuit level and above. They include circuit designs, as detailed in chapter 3, as well as the validation of a more complex image filter demonstrator, which is discussed in chapter 4. At the highest level, a system-level benchmarking platform was realized to help predict system performance based on the available device-level simulation and characterization data, as described in chapter 5.

<sup>&</sup>lt;sup>2</sup>Including Atomic Layer Deposition (ALD), Pulsed Laser Deposition (PLD), Physical Vapor Deposition (PVD), Molecular Beam Deposition (MBD)

## Chapter 2

# Ferroelectrics: behavior and modeling

| Contents |       |                                                              |           |

|----------|-------|--------------------------------------------------------------|-----------|

| 2.1      | Ferro | electricity                                                  | 23        |

|          | 2.1.1 | Ferroelectric crystals                                       | 23        |

|          | 2.1.2 | <i>P-V</i> curve                                             | 27        |

|          | 2.1.3 | Relationship with capacitance and paraelectricity            | 27        |

|          | 2.1.4 | PUND measurements                                            | 30        |

| 2.2      | Mode  | eling                                                        | 34        |

|          | 2.2.1 | Landau model                                                 | 34        |

|          | 2.2.2 | Preisach model                                               | 37        |

|          | 2.2.3 | Simplified model for large-scale simulation                  | 43        |

| 2.3      | Ferro | pelectric capacitors                                         | 44        |

|          | 2.3.1 | Regular capacitor                                            | 44        |

|          | 2.3.2 | Non-volatility                                               | 44        |

|          | 2.3.3 | Negative capacitance                                         | 45        |

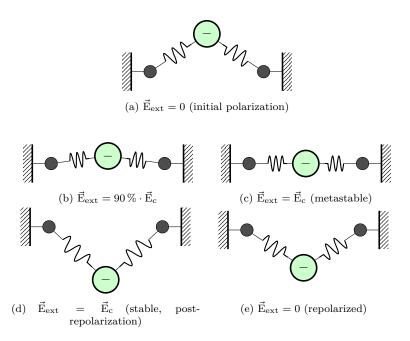

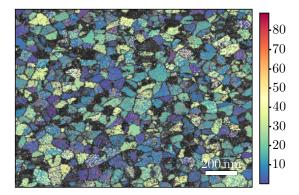

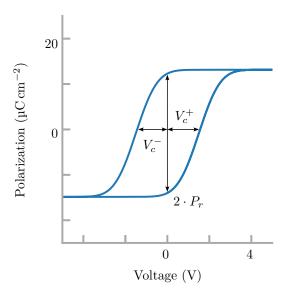

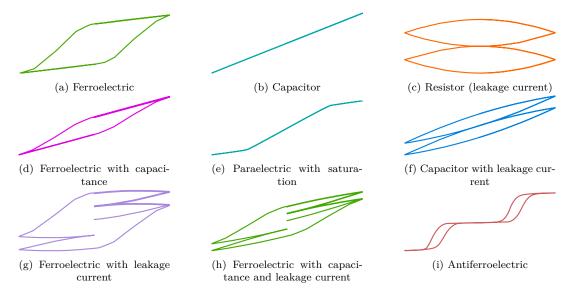

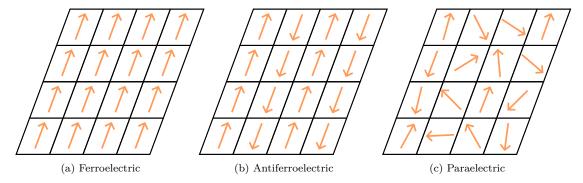

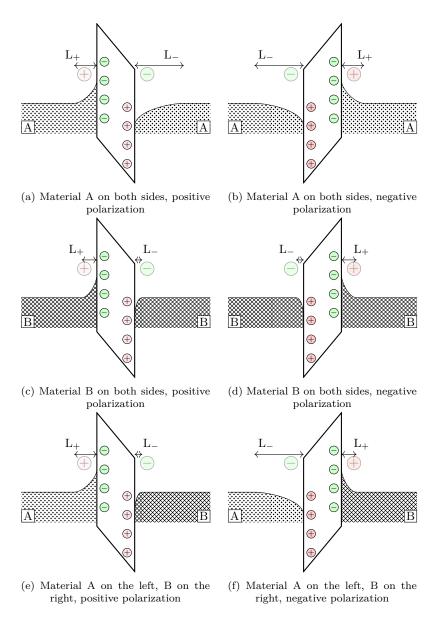

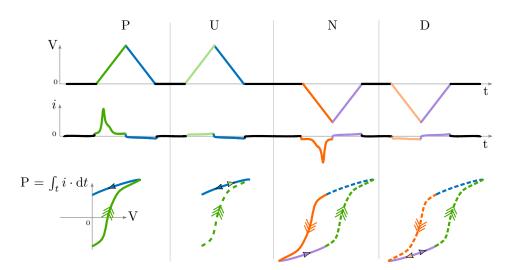

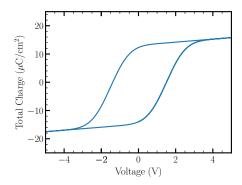

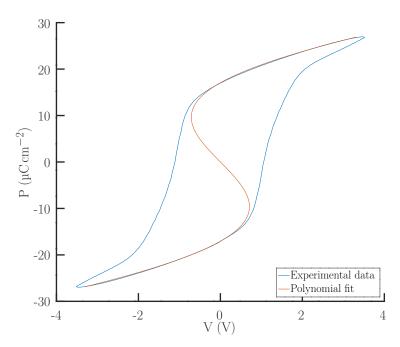

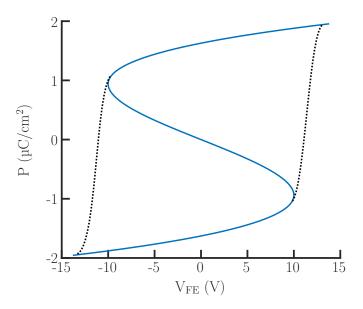

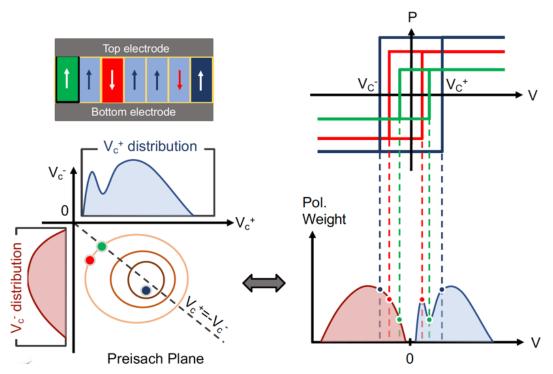

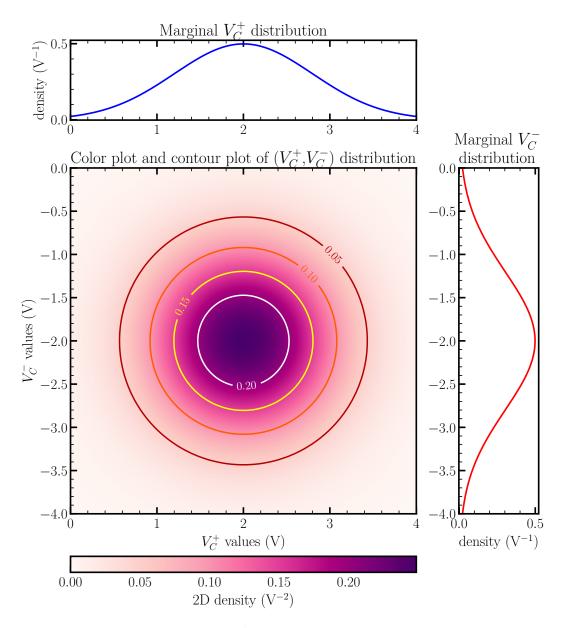

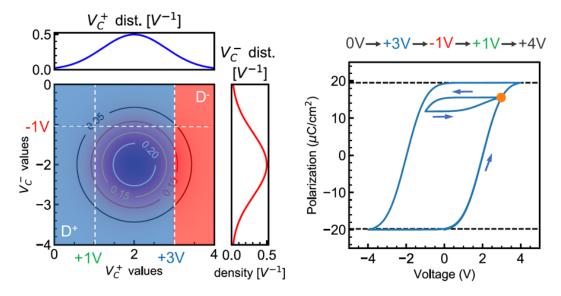

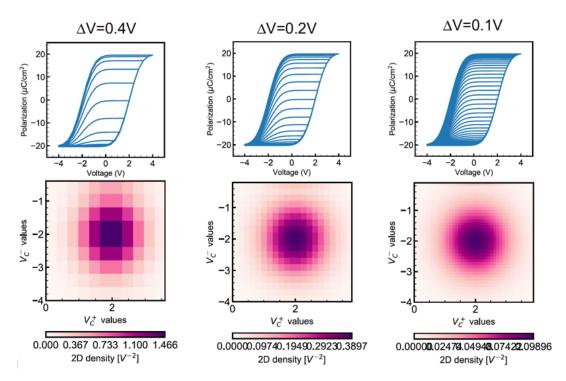

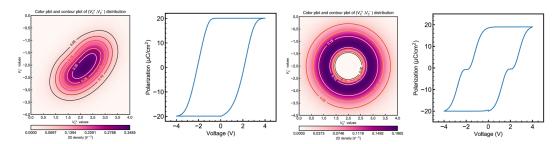

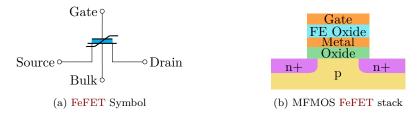

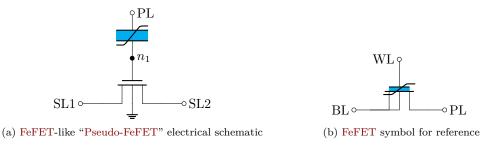

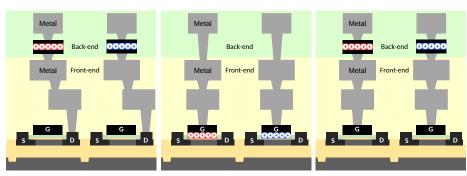

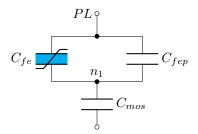

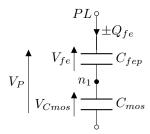

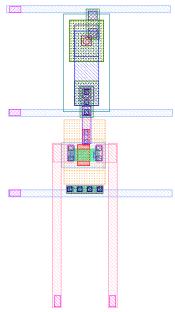

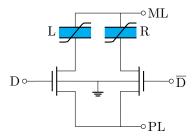

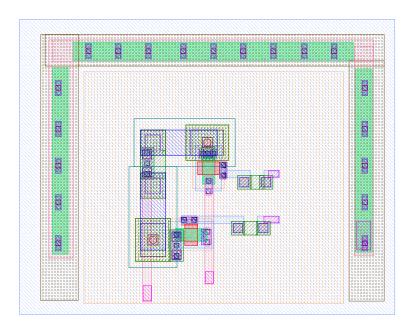

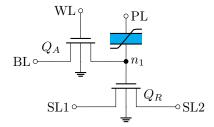

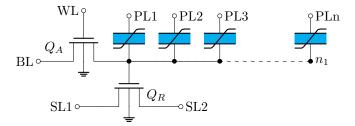

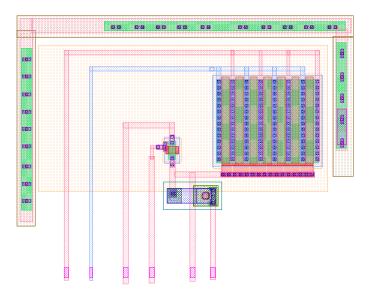

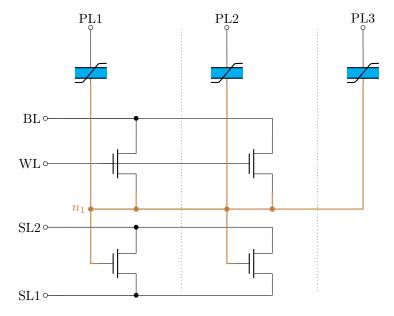

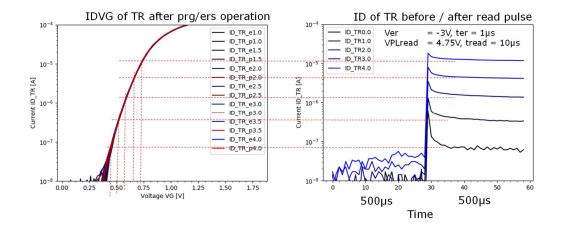

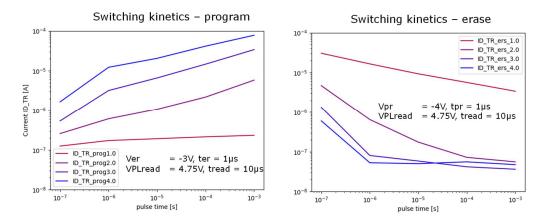

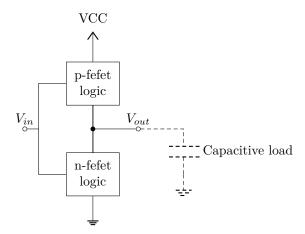

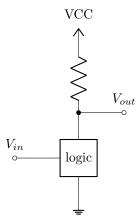

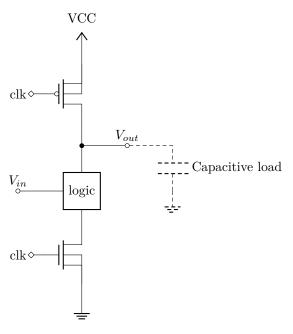

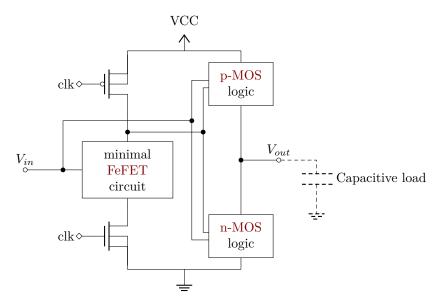

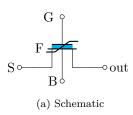

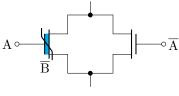

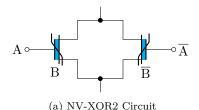

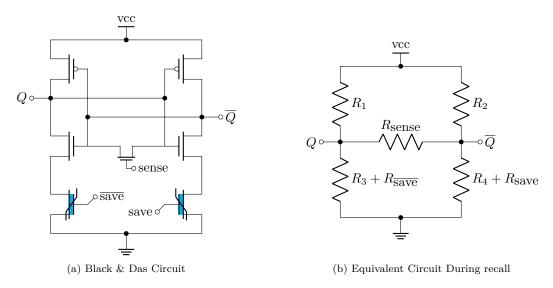

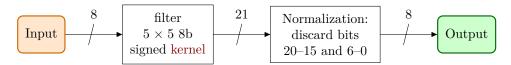

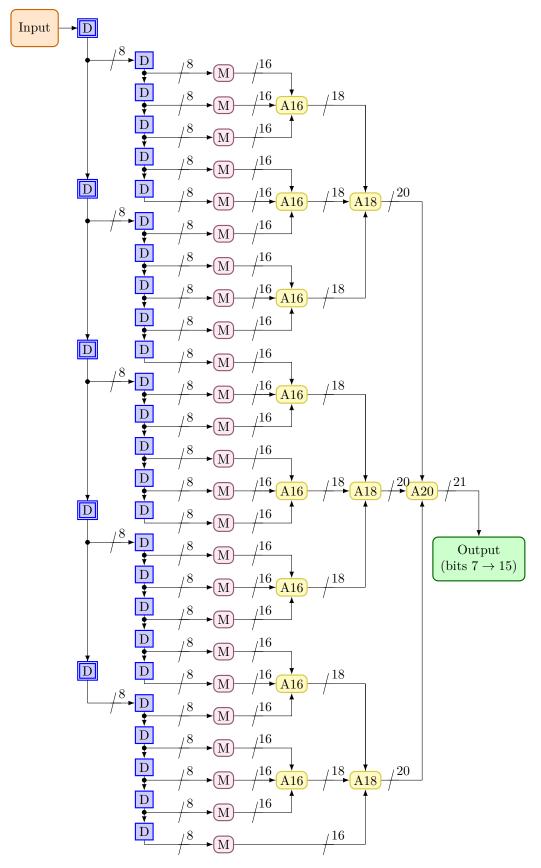

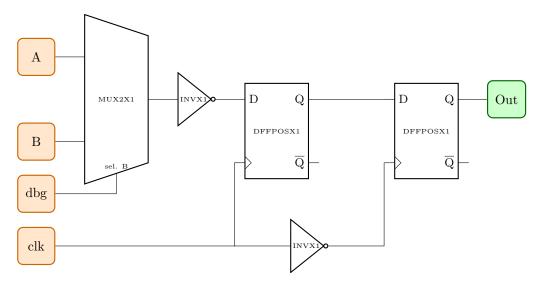

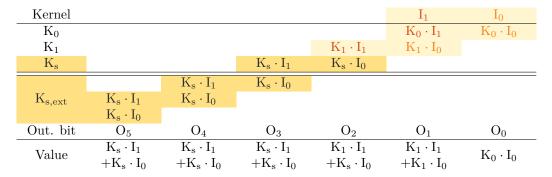

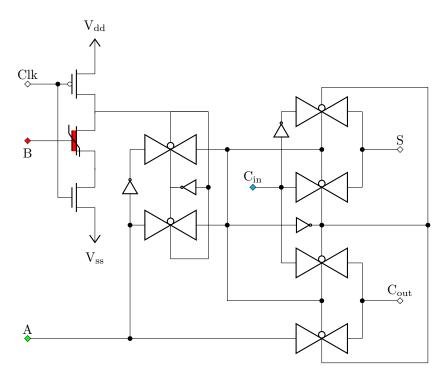

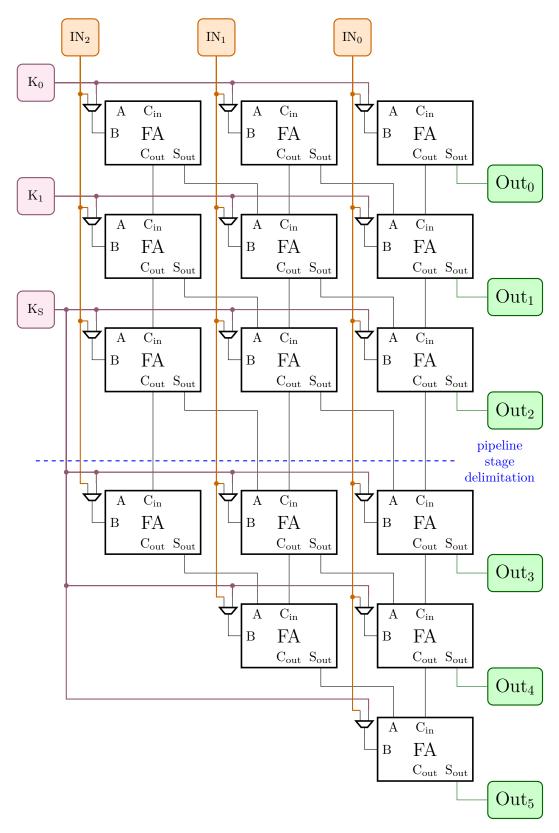

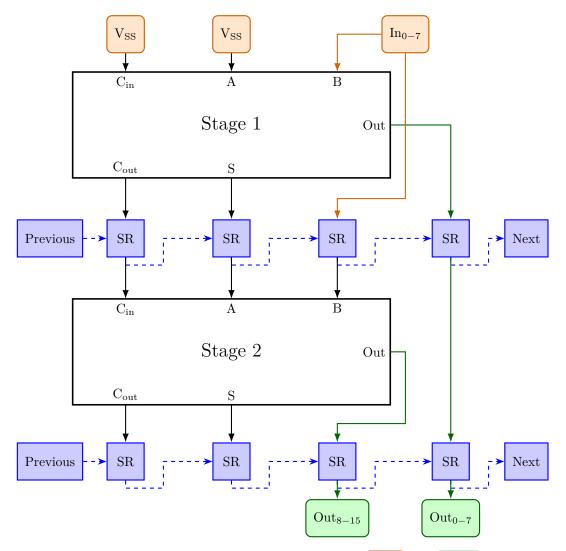

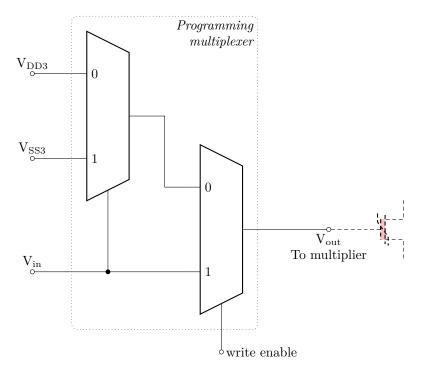

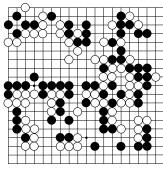

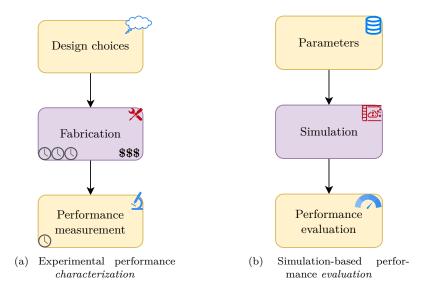

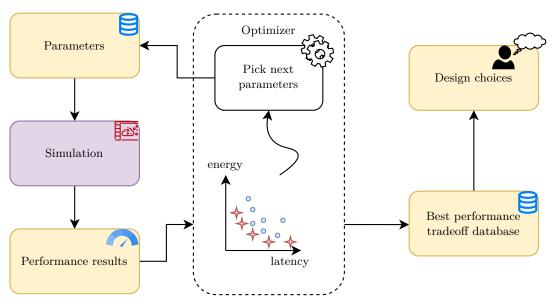

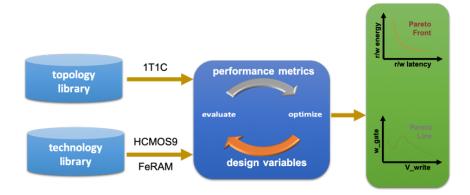

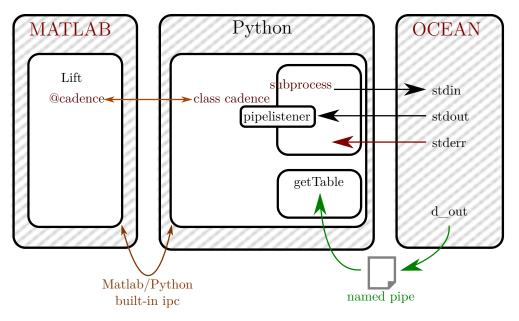

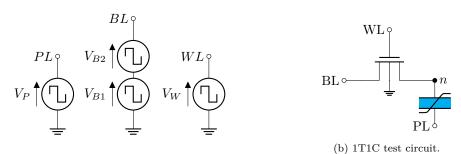

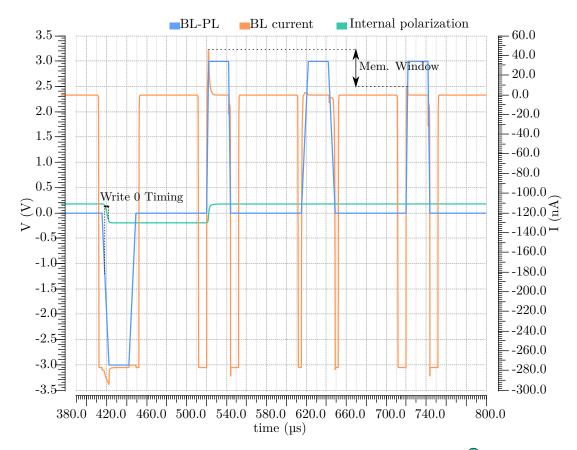

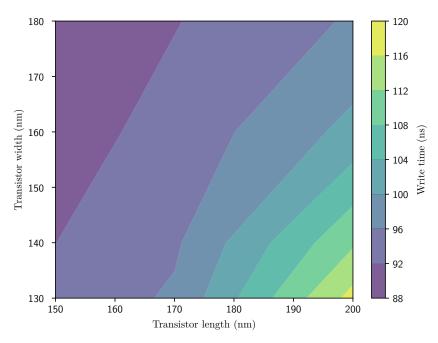

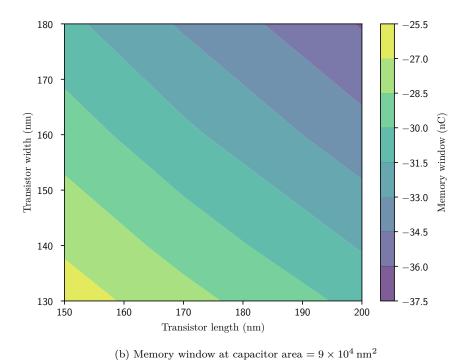

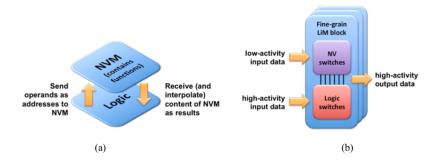

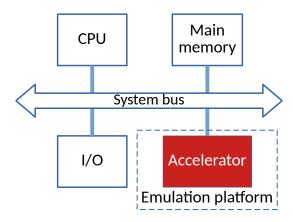

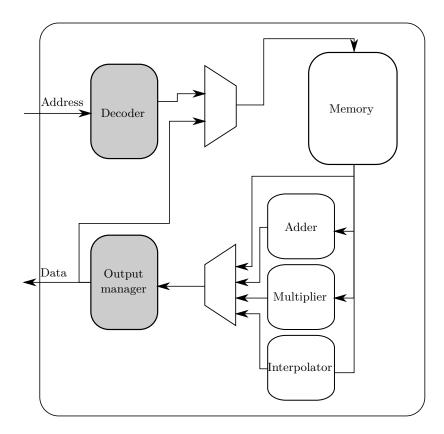

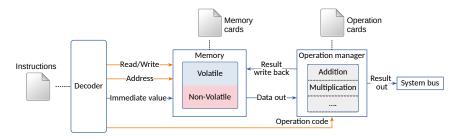

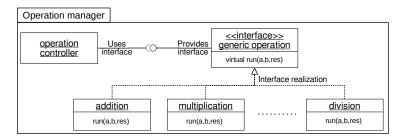

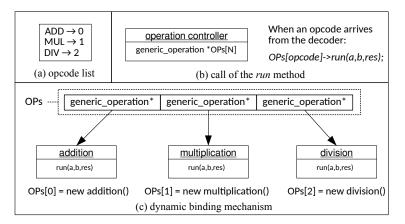

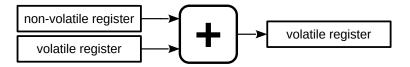

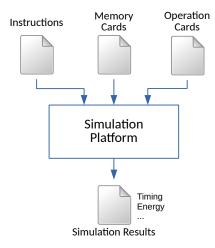

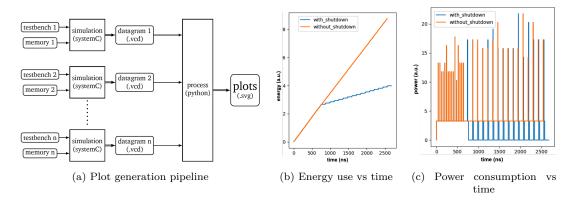

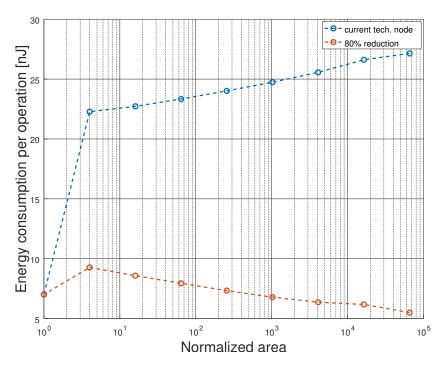

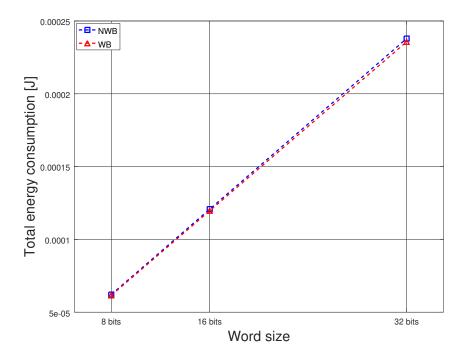

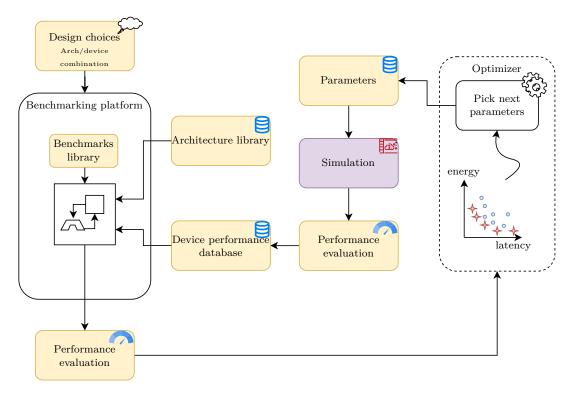

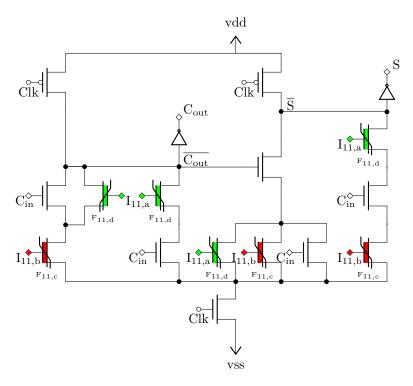

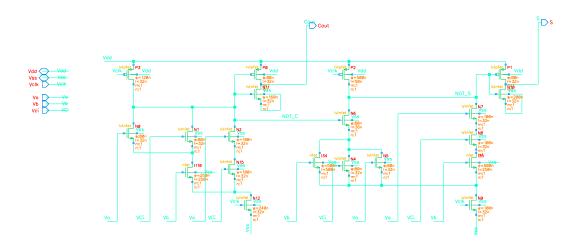

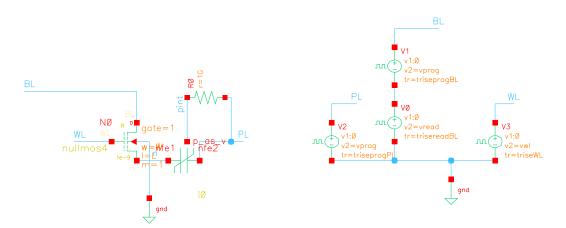

| 2.4      | Ferro | pelectric transistors                                        | <b>45</b> |